AD5695R Overview

Key Specifications

Package: TSSOP

Pins: 16

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 2.7 V

Description

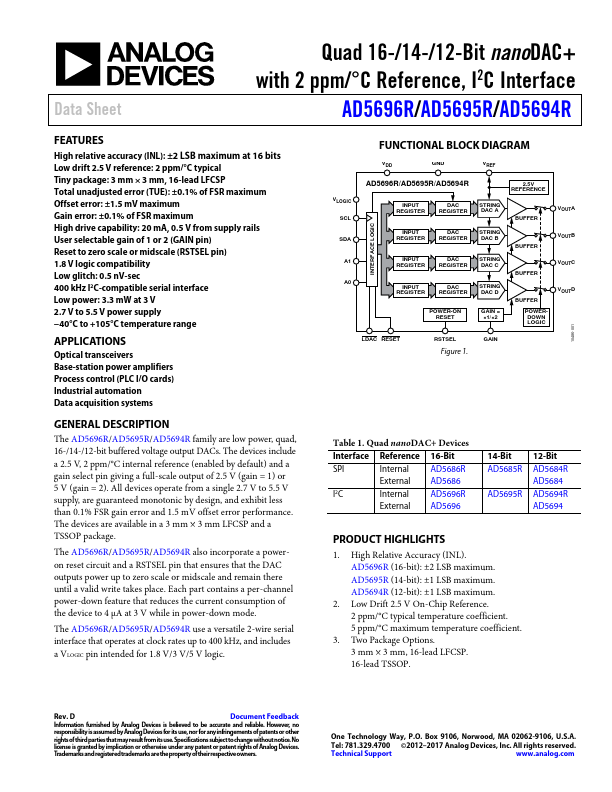

The AD5696R/AD5695R/AD5694R family are low power, quad, 16-/14-/12-bit buffered voltage output DACs. The devices include a 2.5 V, 2 ppm/°C internal reference (enabled by default) and a gain select pin giving a full-scale output of 2.5 V (gain = 1) or 5 V (gain = 2).