AD585

AD585 is High Speed/ Precision Sample-and-Hold Amplifier manufactured by Analog Devices.

- Part of the AD5 comparator family.

- Part of the AD5 comparator family.

a

Features

3.0 s Acquisition Time to ؎0.01% max Low Droop Rate: 1.0 m V/ms max Sample/Hold Offset Step: 3 m V max Aperture Jitter: 0.5 ns Extended Temperature Range:

- 55؇ C to +125؇ C Internal Hold Capacitor Internal Application Resistors ؎12 V or ؎15 V Operation Available in Surface Mount APPLICATIONS Data Acquisition Systems Data Distribution Systems Analog Delay & Storage Peak Amplitude Measurements MIL-STD-883 pliant Versions Available PRODUCT DESCRIPTION

High Speed, Precision Sample-and-Hold Amplifier AD585

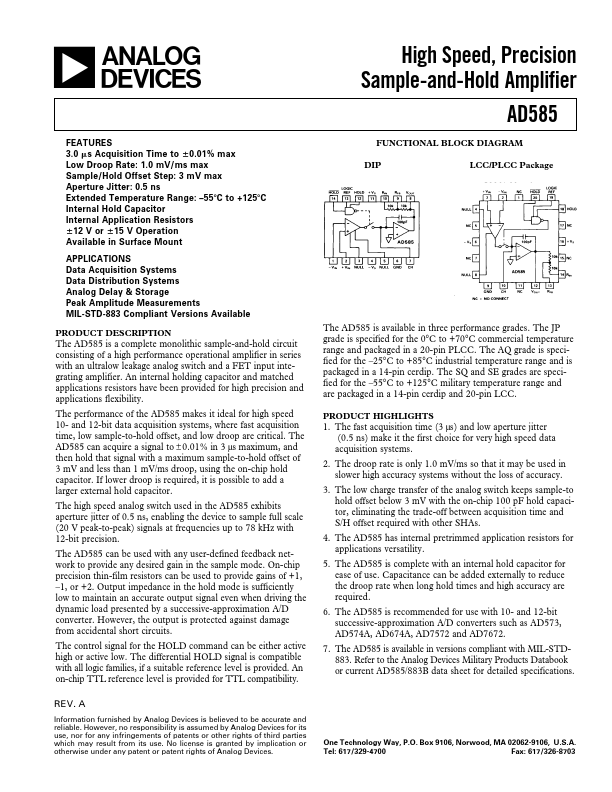

FUNCTIONAL BLOCK DIAGRAM DIP LCC/PLCC Package

The AD585 is a plete monolithic sample-and-hold circuit consisting of a high performance operational amplifier in series with an ultralow leakage analog switch and a FET input integrating amplifier. An internal holding capacitor and matched applications resistors have been provided for high precision and applications flexibility. The performance of the AD585 makes it ideal for high speed 10- and 12-bit data acquisition systems, where fast acquisition time, low sample-to-hold offset, and low droop are critical. The AD585 can acquire a signal to ± 0.01% in 3 µs maximum, and then hold that signal with a maximum sample-to-hold offset of 3 m V and less than 1 m V/ms droop, using the on-chip hold capacitor. If lower droop is required, it is possible to add a larger external hold capacitor. The high speed analog switch used in the AD585 exhibits aperture jitter of 0.5 ns, enabling the device to sample full scale (20 V peak-to-peak) signals at frequencies up to 78 k Hz with 12-bit precision. The AD585 can be used with any user-defined feedback network to provide any desired gain in the sample mode. On-chip precision thin-film resistors can be used to provide gains of +1,

- 1, or +2. Output impedance in the hold mode is sufficiently low to maintain an accurate output signal even when driving the dynamic load presented by a successive-approximation A/D converter. However, the output is protected against damage from...