AD6684

AD6684 is 135MHz Quad IF Receiver manufactured by Analog Devices.

Data Sheet

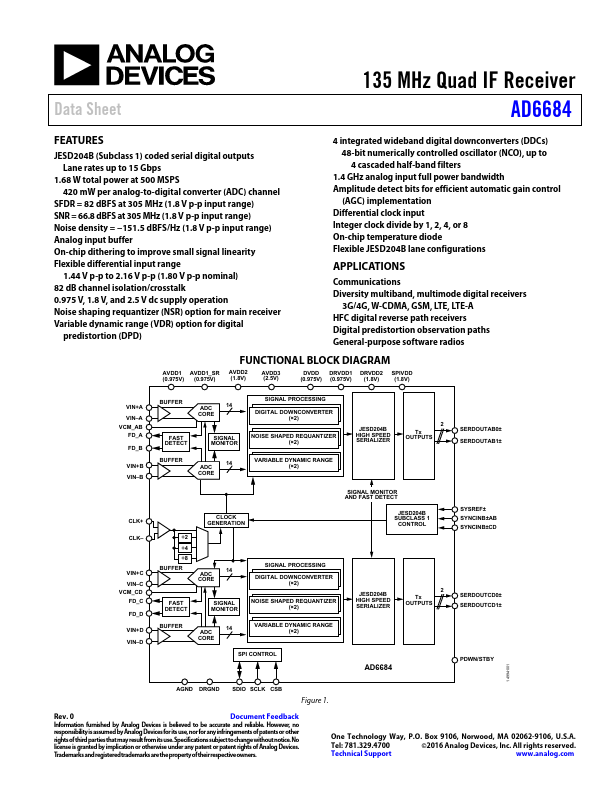

135 MHz Quad IF Receiver AD6684

Features

JESD204B (Subclass 1) coded serial digital outputs Lane rates up to 15 Gbps

1.68 W total power at 500 MSPS 420 mW per analog-to-digital converter (ADC) channel

SFDR = 82 dBFS at 305 MHz (1.8 V p-p input range) SNR = 66.8 dBFS at 305 MHz (1.8 V p-p input range) Noise density =

- 151.5 dBFS/Hz (1.8 V p-p input range) Analog input buffer On-chip dithering to improve small signal linearity Flexible differential input range

1.44 V p-p to 2.16 V p-p (1.80 V p-p nominal) 82 dB channel isolation/crosstalk 0.975 V, 1.8 V, and 2.5 V dc supply operation Noise shaping requantizer (NSR) option for main receiver Variable dynamic range (VDR) option for...