AD7175-8

AD7175-8 is SigmaDelta ADC manufactured by Analog Devices.

FEATURES

GENERAL DESCRIPTION

Fast and flexible output rate: 5 SPS to 250 k SPS Channel scan data rate of 50 k SPS/channel (20 µs settling) Performance specifications

17.2 noise free bits at 250 k SPS 20.2 noise free bits at 2.5 k SPS 24 noise free bits at 20 SPS INL: ±1 ppm of FSR 85 d B filter rejection of 50 Hz and 60 Hz with 50 ms settling User configurable input channels 8 fully differential channels or 16 single-ended channels Crosspoint multiplexer On-chip 2.5 V reference (±2 ppm/°C drift) True rail-to-rail analog and reference input buffers Internal or external clock Power supply: AVDD1

- AVSS = 5 V, AVDD2 = IOVDD = 2 V to 5 V (nominal) Split supply with AVDD1/AVSS at ±2.5 V ADC current: 8.4 m A Temperature range:

- 40°C to +105°C 3- or 4-wire serial digital interface (Schmitt trigger on SCLK) Serial port interface (SPI), QSPI, MICROWIRE, and DSP patible

APPLICATIONS

Process control: PLC/DCS modules Temperature and pressure measurement

Medical and scientific multichannel instrumentation Chromatography

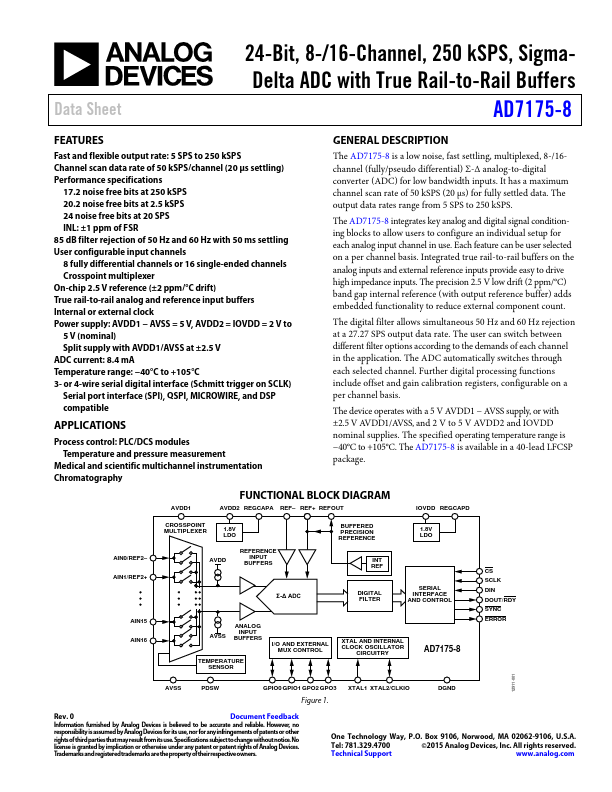

The AD7175-8 is a low noise, fast settling, multiplexed, 8-/16channel (fully/pseudo differential) Σ-Δ analog-to-digital converter (ADC) for low bandwidth inputs. It has a maximum channel scan rate of 50 k SPS (20 µs) for fully settled data. The output data rates range from 5 SPS to 250 k SPS.

The AD7175-8 integrates key analog and digital signal conditioning blocks to allow users to configure an individual setup for each analog input channel in use. Each feature can be user selected on a per channel basis. Integrated true rail-to-rail buffers on the analog inputs and external reference inputs provide easy to drive high impedance inputs. The precision 2.5 V low drift (2 ppm/°C) band gap internal reference (with output reference buffer) adds embedded functionality to reduce external ponent count.

The digital filter allows simultaneous 50 Hz and 60 Hz rejection at a 27.27 SPS output data rate. The user can switch between different filter options according to the demands...