AD9267

AD9267 is 640 MSPS Dual Continuous Time Sigma-Delta Modulator manufactured by Analog Devices.

10 MHz Bandwidth, 640 MSPS Dual Continuous Time Sigma-Delta Modulator

Features

SNR: 83 dB (85 dBFS) to 10 MHz input SFDR:

- 88 dBc to 10 MHz input Noise figure: 15 dB Input impedance: 1 kΩ Power: 416 mW 10 MHz real or 20 MHz plex bandwidth 1.8 V analog supply operation On-chip PLL clock multiplier On-chip voltage reference Twos plement data format 640 MSPS, 4-bit LVDS data output Serial control interface (SPI)

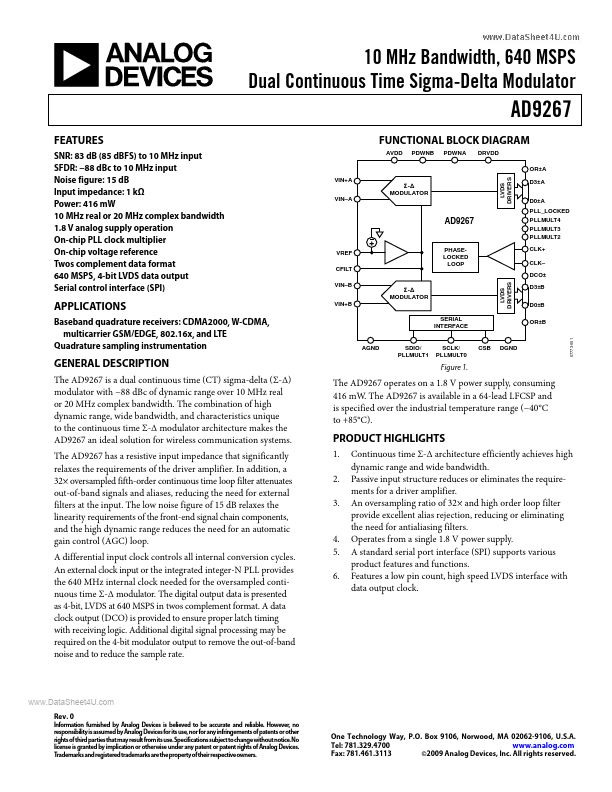

FUNCTIONAL BLOCK DIAGRAM

AVDD PDWNB PDWNA DRVDD OR±A VIN+A VIN- A

LVDS DRIVERS

Σ -Δ MODULATOR

D3±A D0±A PLL_LOCKED PLLMULT4 PLLMULT3 PLLMULT2 CLK+ CLK- DCO±

VREF CFILT VIN- B VIN+B Σ -Δ MODULATOR

PHASELOCKED LOOP

LVDS DRIVERS

D3±B D0±B OR±B

07773-001

APPLICATI...