AD9559

Description

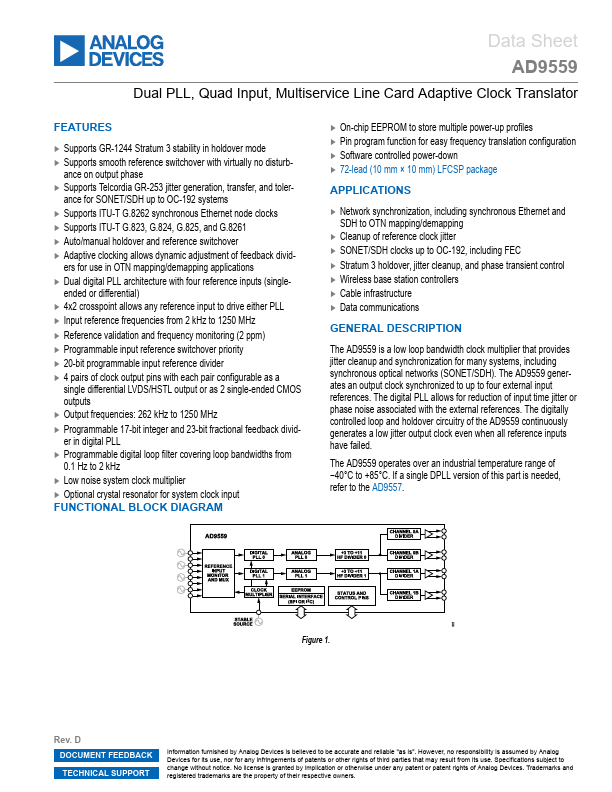

The AD9559 is a low loop bandwidth clock multiplier that provides jitter cleanup and synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9559 generates an output clock synchronized to up to four external input references.

Key Features

- Supports GR-1244 Stratum 3 stability in holdover mode

- Supports smooth reference switchover with virtually no disturb- ance on output phase

- Supports Telcordia GR-253 jitter generation, transfer, and toler- ance for SONET/SDH up to OC-192 systems

- Supports ITU-T G.8262 synchronous Ethernet node clocks

- Auto/manual holdover and reference switchover

- Adaptive clocking allows dynamic adjustment of feedback divid- ers for use in OTN mapping/demapping applications

- Dual digital PLL architecture with four reference inputs (single- ended or differential)

- 4x2 crosspoint allows any reference input to drive either PLL

- Input reference frequencies from 2 kHz to 1250 MHz

- Reference validation and frequency monitoring (2 ppm)