AD9608

Overview

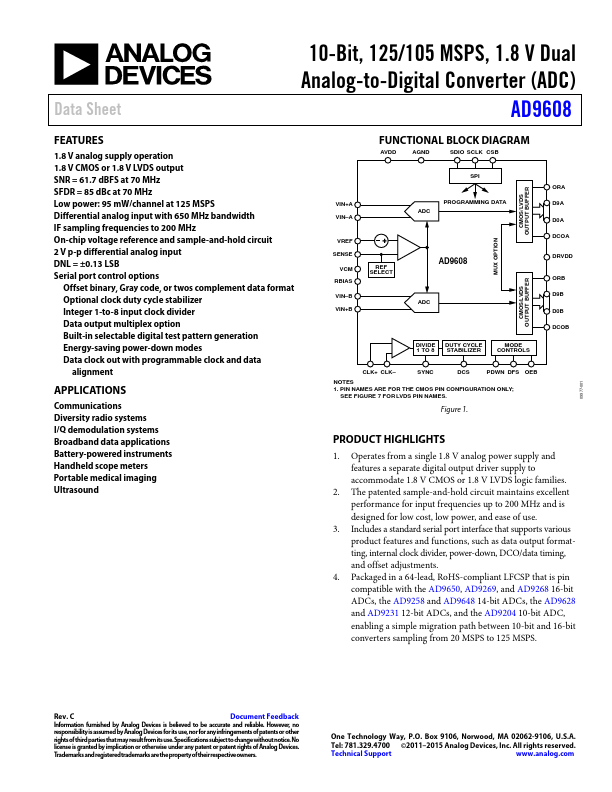

- 8 V analog supply operation 1.8 V CMOS or 1.8 V LVDS output SNR = 61.7 dBFS at 70 MHz SFDR = 85 dBc at 70 MHz Low power: 95 mW/channel at 125 MSPS Differential analog input with 650 MHz bandwidth IF sampling frequencies to 200 MHz On-chip voltage reference and sample-and-hold circuit 2 V p-p differential analog input DNL = ±0.13 LSB Serial port control options Offset binary, Gray code, or twos complement data format Optional clock duty cycle stabilizer Integer 1-to-8 input clock divider Data output multiplex option Built-in selectable digital test pattern generation Energy-saving power-down modes Data clock out with programmable clock and data alignment