AD9600

Overview

- 2. 3. 4.

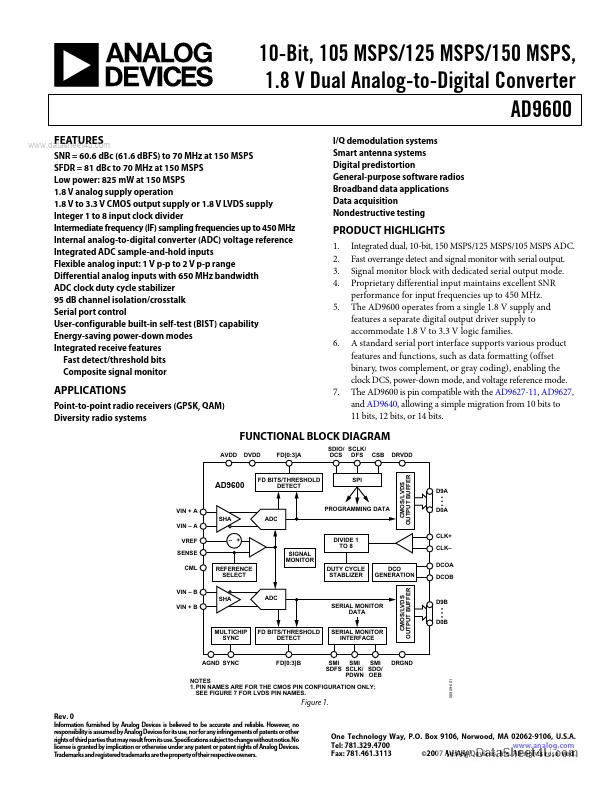

- Integrated dual, 10-bit, 150 MSPS/125 MSPS/105 MSPS ADC. Fast overrange detect and signal monitor with serial output. Signal monitor block with dedicated serial output mode. Proprietary differential input maintains excellent SNR performance for input frequencies up to 450 MHz. The AD9600 operates from a single 1.8 V supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families. A standard serial port interface supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down mode, and voltage reference mode. The AD9600 is pin compatible with the AD9627-11, AD9627, and AD9640, allowing a simple migration from 10 bits to 11 bits, 12 bits, or 14 bits.