AD9862

AD9862 is Mixed-Signal Front-End (MxFE) Processor for Broadband Communications manufactured by Analog Devices.

- Part of the AD9 comparator family.

- Part of the AD9 comparator family.

a

Mixed-Signal Front-End (MxFE™) Processor for Broadband munications AD9860/AD9862-

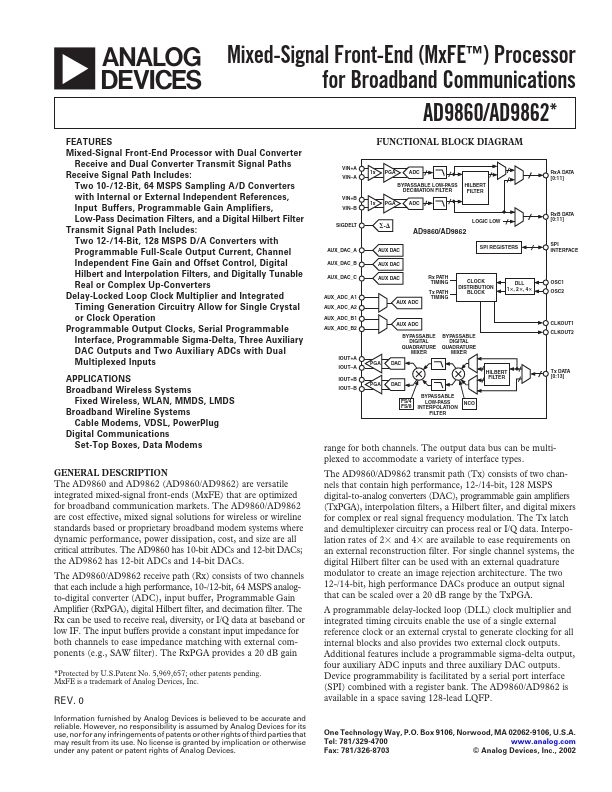

FUNCTIONAL BLOCK DIAGRAM

VIN+A VIN- A 1x PGA ADC BYPASSABLE LOW-PASS DECIMATION FILTER VIN+B VIN- B SIGDELT 1x PGA ADC RxB DATA [0:11] HILBERT FILTER RxA DATA [0:11]

Features

Mixed-Signal Front-End Processor with Dual Converter Receive and Dual Converter Transmit Signal Paths Receive Signal Path Includes: Two 10-/12-Bit, 64 MSPS Sampling A/D Converters with Internal or External Independent References, Input Buffers, Programmable Gain Amplifiers, Low-Pass Decimation Filters, and a Digital Hilbert Filter Transmit Signal Path Includes: Two 12-/14-Bit, 128 MSPS D/A Converters with Programmable Full-Scale...