AD9861

AD9861 is Mixed-Signal Front-End (MxFE-TM) Baseband Transceiver manufactured by Analog Devices.

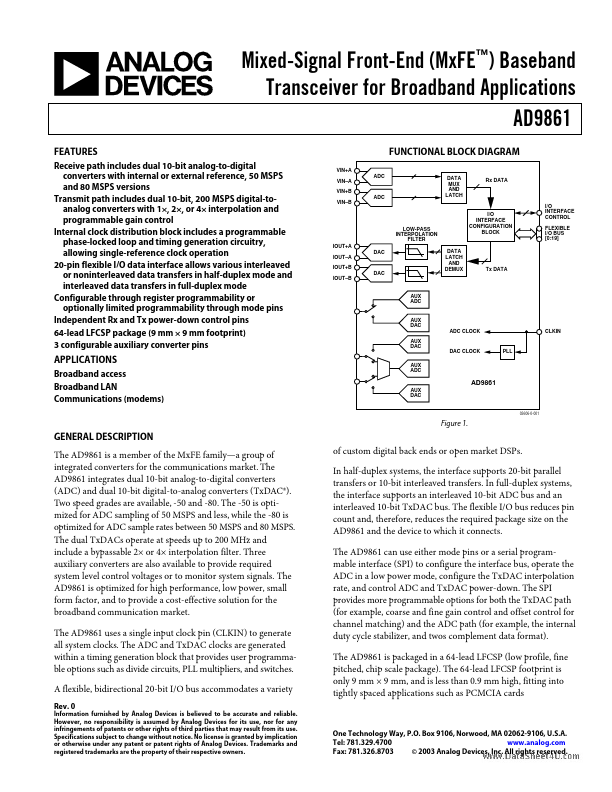

Mixed-Signal Front-End (MxFE™) Baseband Transceiver for Broadband Applications AD9861

Features

Receive path includes dual 10-bit analog-to-digital converters with internal or external reference, 50 MSPS and 80 MSPS versions Transmit path includes dual 10-bit, 200 MSPS digital-toanalog converters with 1×, 2×, or 4× interpolation and programmable gain control Internal clock distribution block includes a programmable phase-locked loop and timing generation circuitry, allowing single-reference clock operation 20-pin flexible I/O data interface allows various interleaved or noninterleaved data transfers in half-duplex mode and interleaved data transfers in full-duplex mode Configurable through...