Datasheet Summary

a

Features

140 MSPS Maximum Conversion Rate 500 MHz Analog Bandwidth 0.5 V to 1.0 V Analog Input Range 400 ps p-p PLL Clock Jitter Power-Down Mode 3.3 V Power Supply 2.5 V to 3.3 V Three-State CMOS Outputs Demultiplexed Output Ports Data Clock Output Provided Low Power: 570 mW Typical Internal PLL Generates CLOCK from HSYNC Serial Port Interface Fully Programmable Supports Alternate Pixel Sampling for Higher-

Resolution Applications

APPLICATIONS RGB Graphics Processing LCD Monitors and Projectors Plasma Display Panels Scan Converters

100 MSPS/140 MSPS Analog Flat Panel Interface

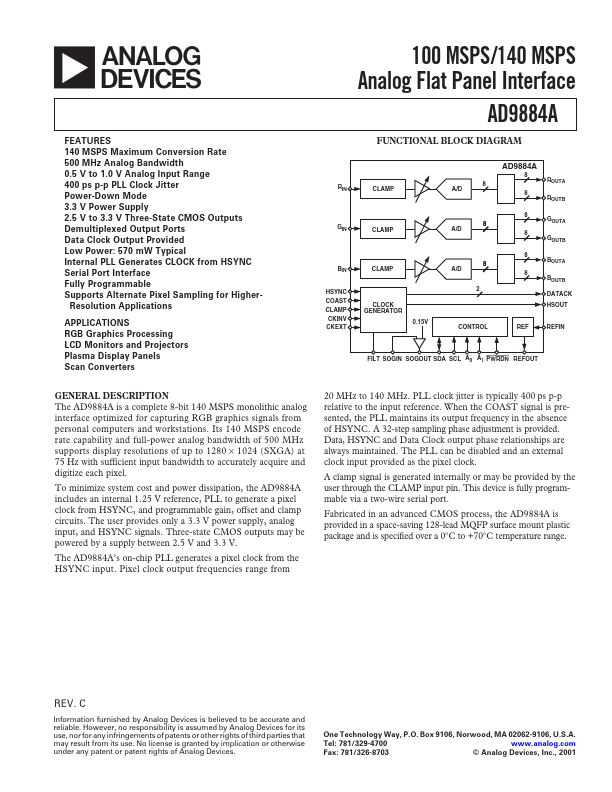

FUNCTIONAL BLOCK DIAGRAM

RIN CLAMP

GIN CLAMP

BIN CLAMP

HSYNC COAST CLAMP CKINV CKEXT

CLOCK...