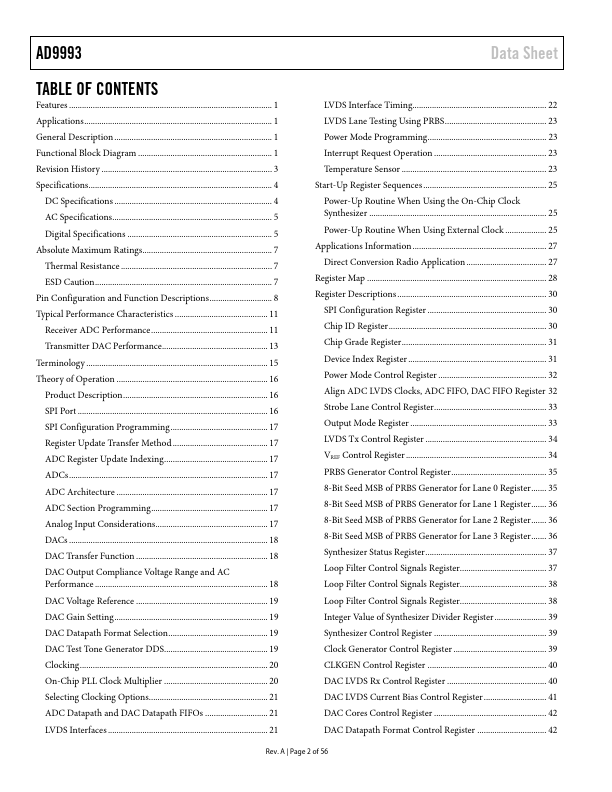

AD9993 Description

The AD9993 is a mixed-signal front-end (MxFE®) device that integrates four 14-bit ADCs and two 14-bit DACs. Figure 1 shows the block diagram of the MxFE. The MxFE is programmable using registers accessed via a serial peripheral interface (SPI).