ADFS7124-8

ADFS7124-8 is 8-Channel 24-Bit Sigma-Delta ADC manufactured by Analog Devices.

Data Sheet ADFS7124-8

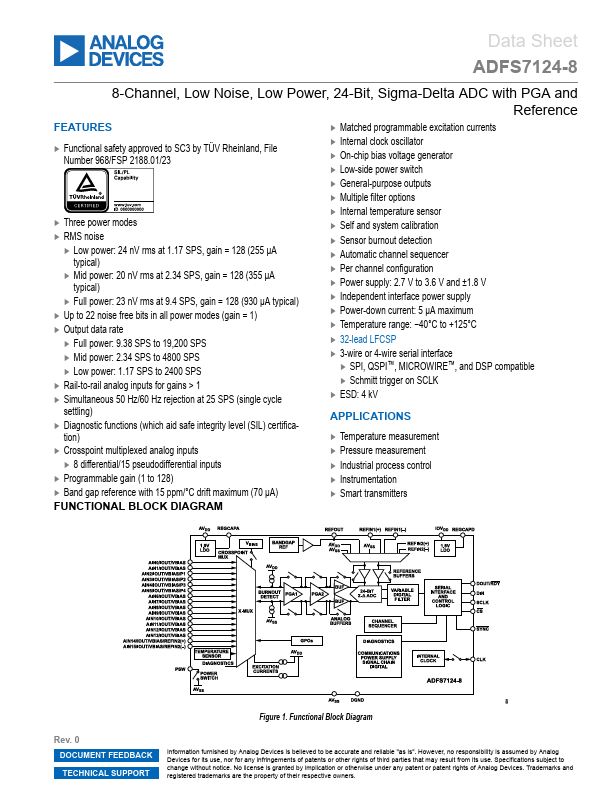

8-Channel, Low Noise, Low Power, 24-Bit, Sigma-Delta ADC with PGA and

Reference

Features

- Functional safety approved to SC3 by TÜV Rheinland, File Number 968/FSP 2188.01/23

- Three power modes

- RMS noise

- Low power: 24 nV rms at 1.17 SPS, gain = 128 (255 µA typical)

- Mid power: 20 nV rms at 2.34 SPS, gain = 128 (355 µA typical)

- Full power: 23 nV rms at 9.4 SPS, gain = 128 (930 µA typical)

- Up to 22 noise free bits in all power modes (gain = 1)

- Output data rate

- Full power: 9.38 SPS to 19,200 SPS

- Mid power: 2.34 SPS to 4800 SPS

- Low power: 1.17 SPS to 2400 SPS

- Rail-to-rail analog inputs for gains > 1

- Simultaneous 50 Hz/60 Hz rejection at 25 SPS...