ADSP-21564

FEATURES

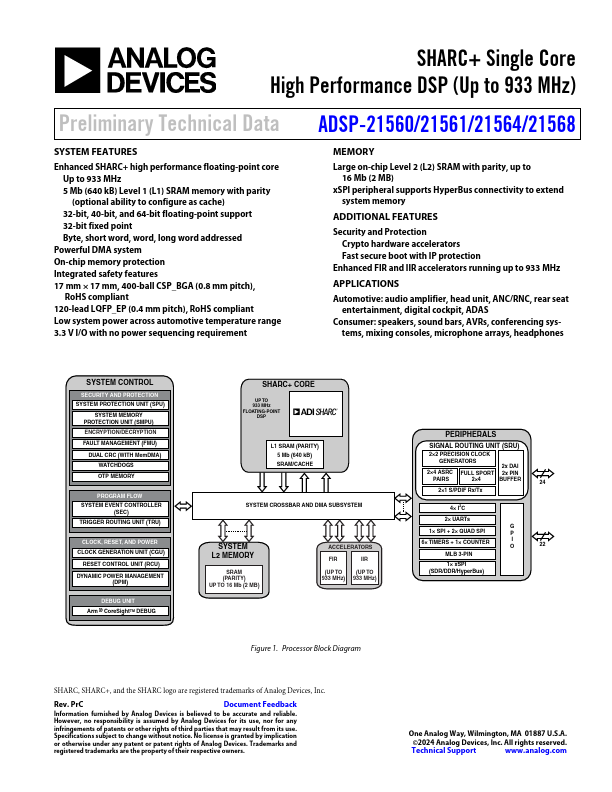

Enhanced SHARC+ high performance floating-point core Up to 933 MHz 5 Mb (640 k B) Level 1 (L1) SRAM memory with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short word, word, long word addressed

Powerful DMA system On-chip memory protection Integrated safety features

17 mm × 17 mm, 400-ball CSP_BGA (0.8 mm pitch),

Ro HS pliant 120-lead LQFP_EP (0.4 mm pitch), Ro HS pliant Low system power across automotive temperature range 3.3 V I/O with no power sequencing requirement

ADSP-21560/21561/21564/21568

MEMORY

Large on-chip Level 2 (L2) SRAM with parity, up to 16 Mb (2 MB) x SPI peripheral supports Hyper Bus connectivity to extend system memory

ADDITIONAL FEATURES

Security and Protection Crypto hardware accelerators Fast secure boot with IP protection

Enhanced FIR and IIR accelerators running up to 933 MHz

APPLICATIONS

Automotive: audio amplifier, head unit, ANC/RNC, rear seat entertainment, digital cockpit,...