ADSP-21566

FEATURES

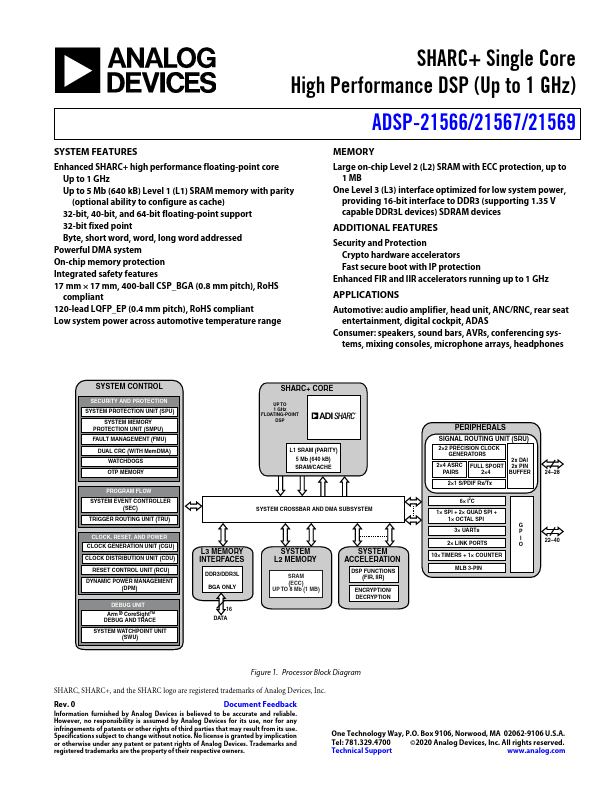

Enhanced SHARC+ high performance floating-point core Up to 1 GHz Up to 5 Mb (640 k B) Level 1 (L1) SRAM memory with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short word, word, long word addressed

Powerful DMA system On-chip memory protection Integrated safety features

17 mm × 17 mm, 400-ball CSP_BGA (0.8 mm pitch), Ro HS pliant 120-lead LQFP_EP (0.4 mm pitch), Ro HS pliant Low system power across automotive temperature range

ADSP-21566/21567/21569

MEMORY

Large on-chip Level 2 (L2) SRAM with ECC protection, up to 1 MB

One Level 3 (L3) interface optimized for low system power, providing 16-bit interface to DDR3 (supporting 1.35 V capable DDR3L devices) SDRAM devices

ADDITIONAL FEATURES

Security and Protection Crypto hardware accelerators Fast secure boot with IP protection

Enhanced FIR and IIR accelerators running up to 1 GHz

APPLICATIONS

Automotive: audio amplifier, head unit, ANC/RNC, rear seat...