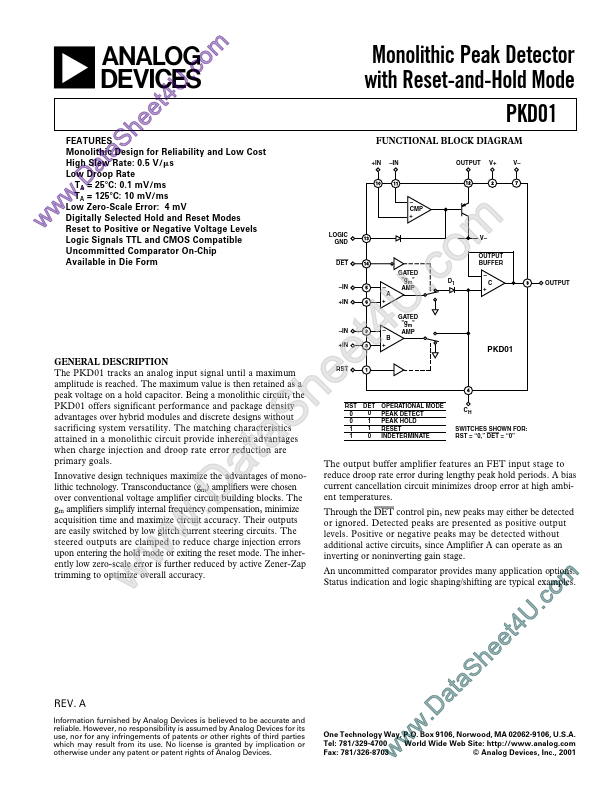

| Part | PKD01 |

|---|---|

| Description | Monolithic Peak Detector with Reset-and-Hold Mode |

| Manufacturer | Analog Devices |

| Size | 429.08 KB |

Pricing from 7.22 USD, available from Aztech and Win Source.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Aztech | 551 | 1+ : 7.22 USD | View Offer |

| Win Source | 5 | - | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| AP9563GH | Advanced Power Electronics Corp | P-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| bq24780S | Texas Instruments | 1- to 4-Cell Hybrid Power Boost Mode Battery Charge Controller |

| B3045G | onsemi | Switch-mode Power Rectifiers |