Datasheet Summary

( DataSheet : .. )

S19235

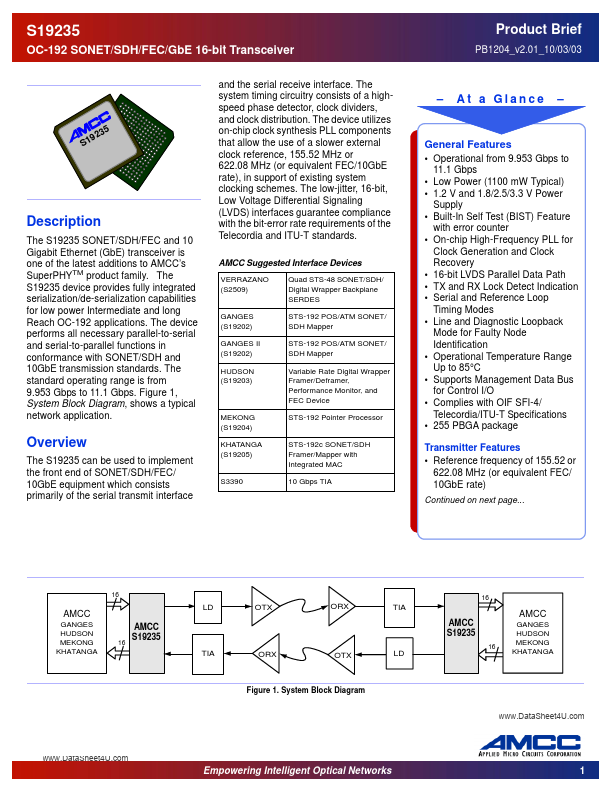

OC-192 SONET/SDH/FEC/GbE 16-bit Transceiver and the serial receive interface. The system timing circuitry consists of a highspeed phase detector, clock dividers, and clock distribution. The device utilizes on-chip clock synthesis PLL ponents that allow the use of a slower external clock reference, 155.52 MHz or 622.08 MHz (or equivalent FEC/10GbE rate), in support of existing system clocking schemes. The low-jitter, 16-bit, Low Voltage Differential Signaling (LVDS) interfaces guarantee pliance with the bit-error rate requirements of the Telecordia and ITU-T standards.

AMCC Suggested Interface Devices

VERRAZANO (S2509) Quad STS-48 SONET/SDH/...