ADS5277

Overview

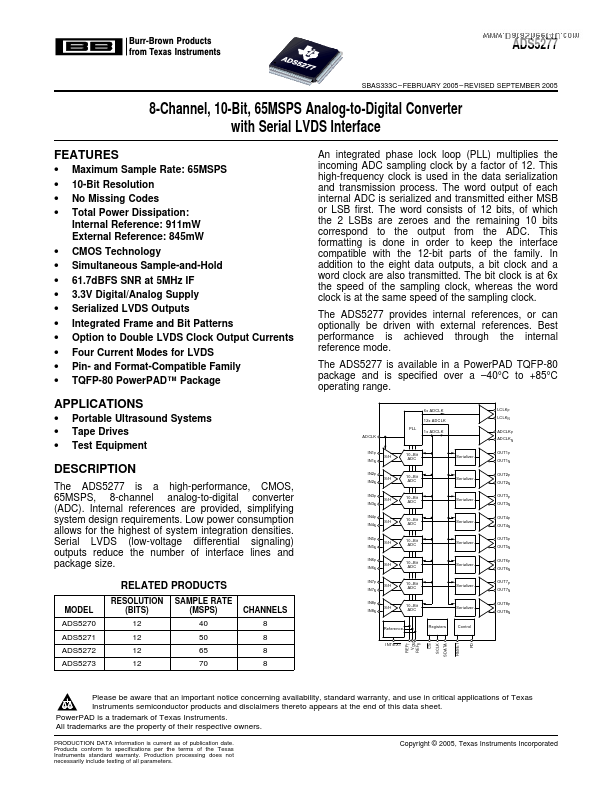

- Maximum Sample Rate: 65MSPS 10-Bit Resolution No Missing Codes Total Power Dissipation: Internal Reference: 911mW External Reference: 845mW CMOS Technology Simultaneous Sample-and-Hold 61.7dBFS SNR at 5MHz IF 3.3V Digital/Analog Supply Serialized LVDS Outputs Integrated Frame and Bit Patterns Option to Double LVDS Clock Output Currents Four Current Modes for LVDS Pin- and Format-Compatible Family TQFP-80 PowerPAD™ Package An integrated phase lock loop (PLL) multiplies the incoming ADC sampling clock by a factor of

- This high-frequency clock is used in the data serialization and transmission process. The word output of each internal ADC is serialized and transmitted either MSB or LSB first. The word consists of 12 bits, of which the 2 LSBs are zeroes and the remaining 10 bits correspond to the output from the ADC. This formatting is done in order to keep the interface compatible with the 12-bit parts of the family. In addition to the eight data outputs, a bit clock and a word clock are also transmitted. The bit clock is at 6x the speed of the sampling clock, whereas the word clock is at the same speed of the sampling clock. The ADS5277 provides internal references, or can optionally be driven with external references. Best performance is achieved through the internal reference mode. The ADS5277 is available in a PowerPAD TQFP-80 package and is specified over a -40°C to +85°C operating range. 6x ADCLK 12x ADCLK PLL ADCLK 1x ADCLK LCLKP LCLKN ADCLK P ADCLK N OUT1 P OUT1 N OUT2 P OUT2 N OUT3 P OUT3 N OUT4 P OUT4 N OUT5 P OUT5 N OUT6 P OUT6 N OUT7 P OUT7 N OUT8 P OUT8 N * * * * * * * * * * * *