CY28401

CY28401 is 100-MHz Differential Buffer manufactured by Cypress.

100-MHz Differential Buffer for PCI Express and SATA

Features

- CK409 or CK410 panion buffer

- Eight differential 0.7v clock pairs

- Individual OE controls

- Low CTC jitter (< 50 ps)

- Programmable bandwidth

- SRC_STOP# power management control

- SMBus Block/Byte/Word Read and Write support

- 3.3V operation

- PLL Bypass-configurable

- Divide by 2 programmable

- 48-pin SSOP package

Functional Description

The CY28401 is a differential buffer and serves as a panion device to the CK409 or CK410 clock generator. The device is capable of distributing the Serial Reference Clock (SRC) in PCI Express and SATA implementations.

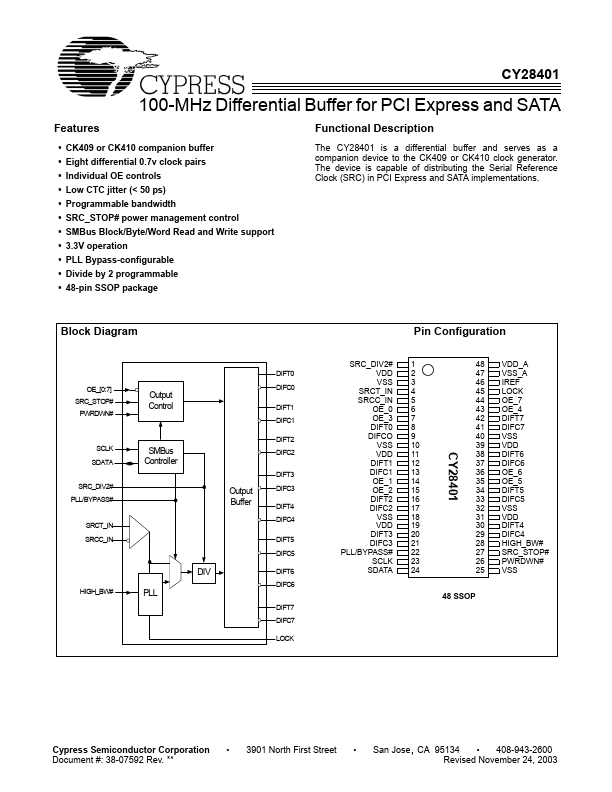

Block Diagram

SRC_DIV2# VDD VSS SRCT_IN SRCC_IN OE_0 OE_3 DIFT0 DIFCO VSS VDD DIFT1 DIFC1 OE_1 OE_2 DIFT2 DIFC2 VSS VDD DIFT3 DIFC3 PLL/BYPASS# SCLK SDATA

Pin Configuration

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 VDD_A VSS_A IREF LOCK OE_7 OE_4 DIFT7 DIFC7 VSS VDD DIFT6 DIFC6 OE_6 OE_5 DIFT5 DIFC5 VSS VDD DIFT4 DIFC4 HIGH_BW# SRC_STOP# PWRDWN# VSS

DIFT0 OE_[0:7] SRC_STOP# PWRDWN#

Output Control

DIFC0 DIFT1 DIFC1 DIFT2

SCLK SDATA SRC_DIV2# PLL/BYPASS# SRCT_IN SRCC_IN

SMBus Controller Output Buffer

DIFC2 DIFT3 DIFC3 DIFT4 DIFC4 DIFT5 DIFC5

HIGH_BW#

DIFT6 DIFC6

48 SSOP

DIFT7 DIFC7 LOCK

Cypress Semiconductor Corporation Document #: 38-07592...