CY7C09289

Key Features

- True dual-ported memory cells which allow simultaneous access of the same memory location

- Six Flow-Through/Pipelined devices - 32K x 16/18 organization (CY7C09279/379) - 64K x 16/18 organization (CY7C09289/389)

- Three Modes - Flow-Through - Pipelined - Burst

- Pipelined output mode on both ports allows fast 100MHz cycle time

- 0.35-micron CMOS for optimum speed/power

- High-speed clock to data access 6.5[1]/7.5/9/12 ns (max.)

- Low operating power - Active = 195 mA (typical) - Standby = 0.05 mA (typical)

- Fully synchronous interface for easier operation

- Burst counters increment addresses internally - Shorten cycle times - Minimize bus noise * * * * *

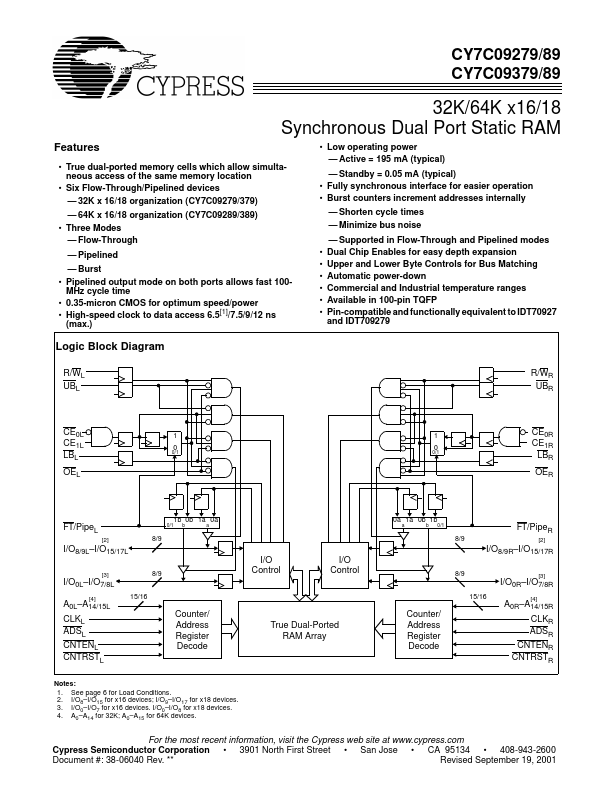

- - Supported in Flow-Through and Pipelined modes Dual Chip Enables for easy depth expansion Upper and Lower Byte Controls for Bus Matching Automatic power-down Commercial and Industrial temperature ranges Available in 100-pin TQFP Pin-compatible and functionally equivalent to IDT70927 and IDT709279 Logic Block Diagram