CY7C1382BV25

Overview

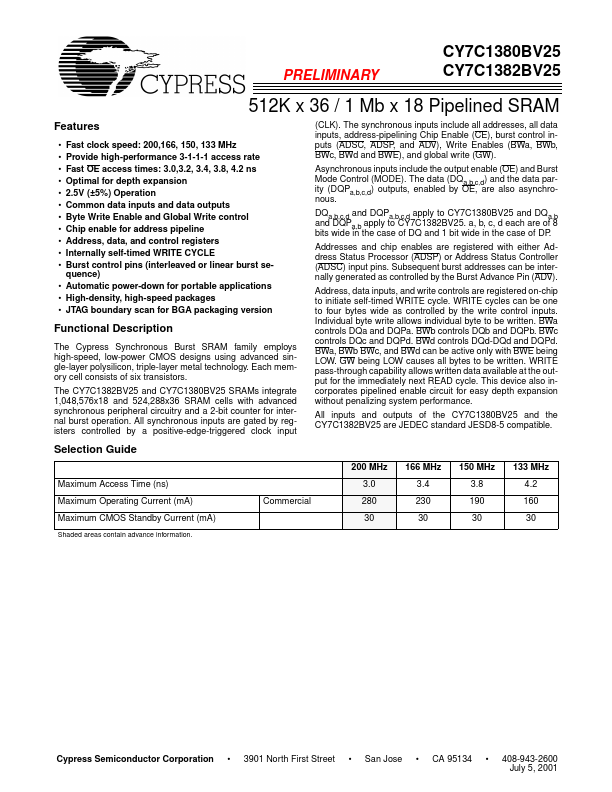

- Fast clock speed: 200,166, 150, 133 MHz

- Provide high-performance 3-1-1-1 access rate

- Fast OE access times: 3.0,3.2, 3.4, 3.8, 4.2 ns

- Optimal for depth expansion

- 2.5V (±5%) Operation

- Common data inputs and data outputs

- Byte Write Enable and Global Write control

- Chip enable for address pipeline

- Address, data, and control registers

- Internally self-timed WRITE CYCLE