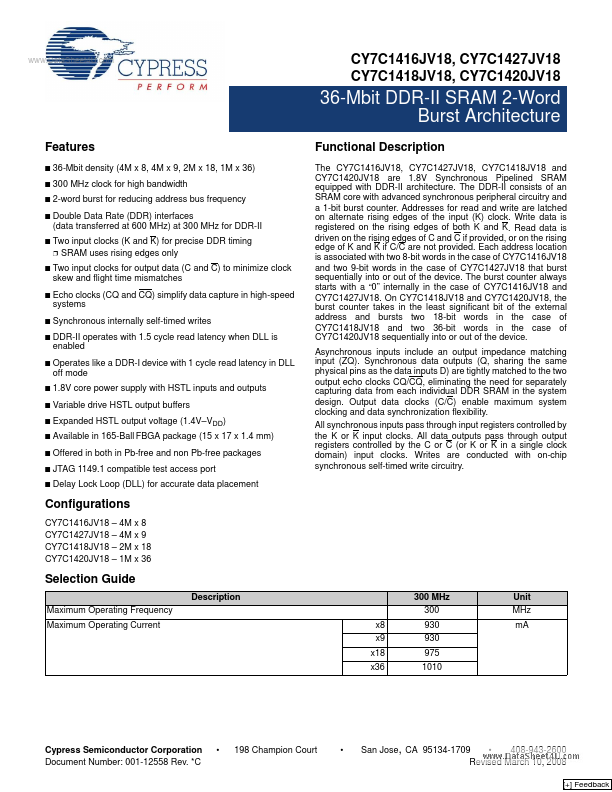

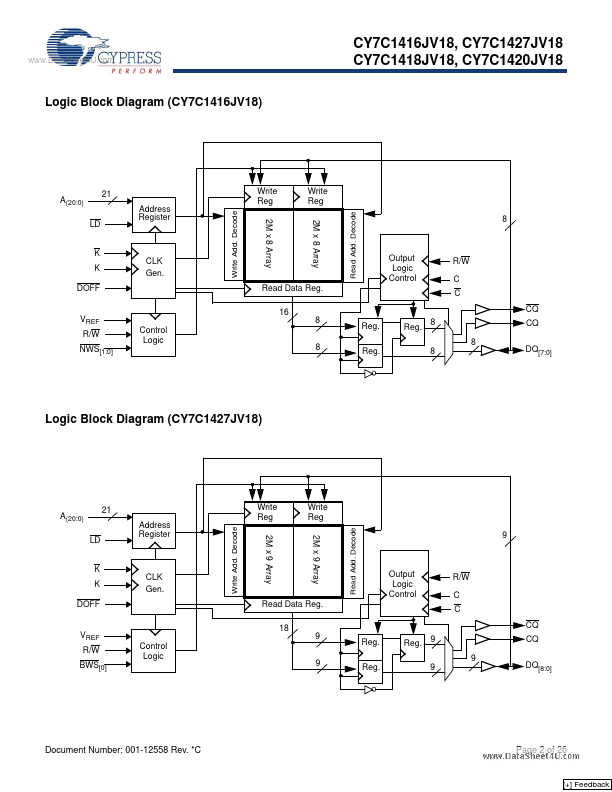

CY7C1427JV18 Description

The DDR-II consists of an SRAM core with advanced synchronous peripheral circuitry and a 1-bit burst counter. Addresses for read and write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K.

CY7C1427JV18 Key Features

- 4M x 8 CY7C1427JV18

- 4M x 9 CY7C1418JV18

- 2M x 18 CY7C1420JV18