CY7C1480BV33

CY7C1480BV33 is (CY7C148xBV33) 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined Sync SRAM manufactured by Cypress.

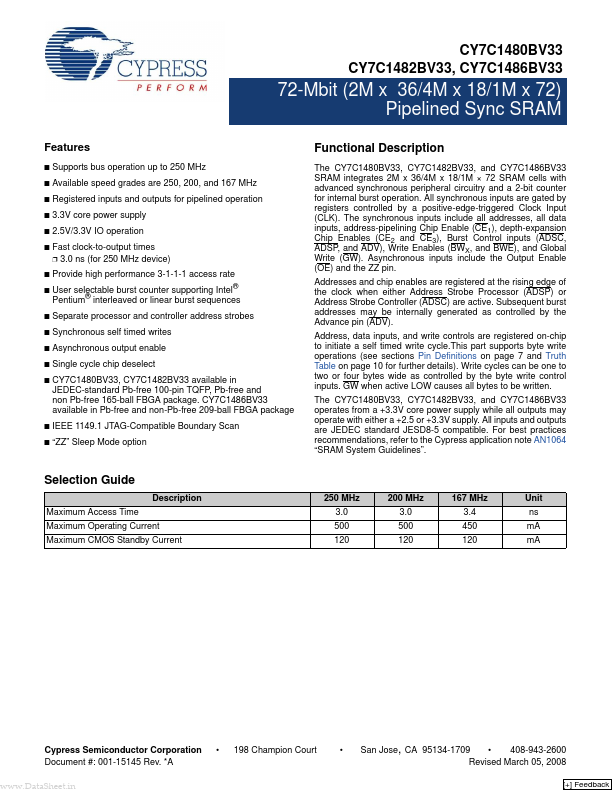

CY7C1480BV33 CY7C1482BV33, CY7C1486BV33

72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined Sync SRAM

Features

- -

- -

- -

Functional Description

The CY7C1480BV33, CY7C1482BV33, and CY7C1486BV33 SRAM integrates 2M x 36/4M x 18/1M × 72 SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining Chip Enable (CE1), depth-expansion Chip Enables (CE2 and CE3), Burst Control inputs (ADSC, ADSP, and ADV), Write Enables (BWX, and BWE), and Global Write (GW). Asynchronous...