CY7C1484V33

CY7C1484V33 is 2M x 36/4M x 18 Pipelined DCD SRAM manufactured by Cypress.

- Part of the CY7 comparator family.

- Part of the CY7 comparator family.

PRELIMINARY

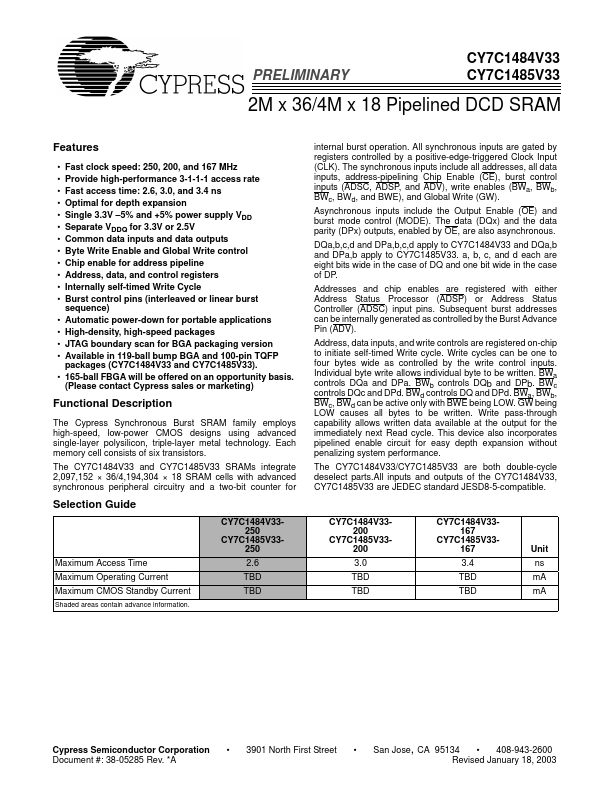

CY7C1484V33 CY7C1485V33

2M x 36/4M x 18 Pipelined DCD SRAM

Features

- -

- -

- -

- -

- -

- -

- -

- -

- Fast clock speed: 250, 200, and 167 MHz Provide high-performance 3-1-1-1 access rate Fast access time: 2.6, 3.0, and 3.4 ns Optimal for depth expansion Single 3.3V

- 5% and +5% power supply VDD Separate VDDQ for 3.3V or 2.5V mon data inputs and data outputs Byte Write Enable and Global Write control Chip enable for address pipeline Address, data, and control registers Internally self-timed Write Cycle Burst control pins (interleaved or linear burst sequence) Automatic power-down for portable applications High-density, high-speed packages JTAG boundary scan for BGA packaging version Available in 119-ball bump BGA and 100-pin TQFP packages (CY7C1484V33 and CY7C1485V33). 165-ball FBGA will be offered on an opportunity basis. (Please contact Cypress sales or marketing) internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining Chip Enable (CE), burst control inputs (ADSC, ADSP, and ADV), write enables (BWa, BWb, BWc, BWd, and BWE), and Global Write (GW). Asynchronous inputs include the Output Enable (OE) and burst mode control (MODE). The data (DQx) and the data parity (DPx) outputs, enabled by OE, are also asynchronous. DQa,b,c,d and DPa,b,c,d apply to CY7C1484V33 and DQa,b and DPa,b apply to CY7C1485V33. a, b, c, and d each are eight bits wide in the case of DQ and one bit wide in the case of DP. Addresses and chip enables are registered with either Address Status Processor (ADSP) or Address Status Controller (ADSC) input pins. Subsequent burst addresses can be internally generated as controlled by the Burst Advance Pin (ADV). Address, data inputs, and write controls are registered on-chip to initiate self-timed Write cycle. Write cycles can be one to four bytes wide as controlled by the write...