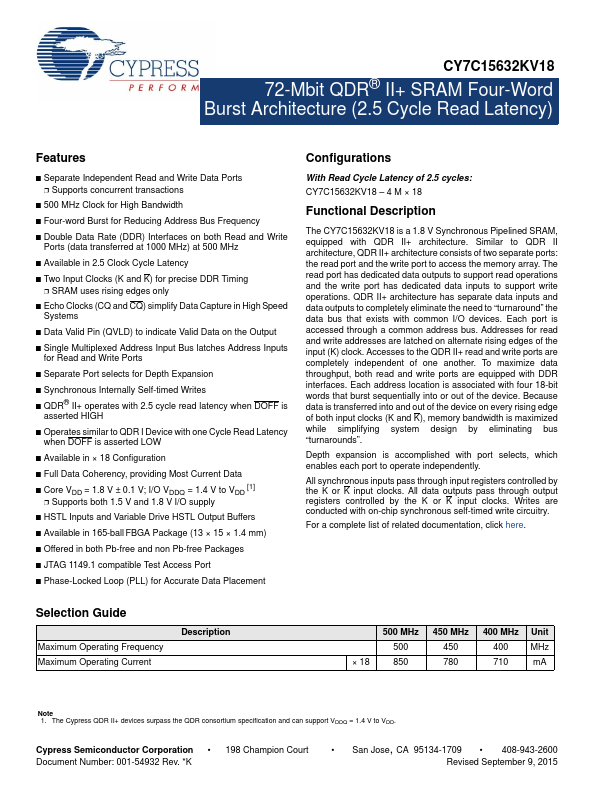

CY7C15632KV18

CY7C15632KV18 is 72-Mbit QDR II+ SRAM Four-Word Burst Architecture manufactured by Cypress.

72-Mbit QDR® II+ SRAM Four-Word Burst Architecture (2.5 Cycle Read Latency)

72-Mbit QDR® II+ SRAM Four-Word Burst Architecture (2.5 Cycle Read Latency)

Features

- Separate Independent Read and Write Data Ports

- Supports concurrent transactions

- 500 MHz Clock for High Bandwidth

- Four-word Burst for Reducing Address Bus Frequency

- Double Data Rate (DDR) Interfaces on both Read and Write Ports (data transferred at 1000 MHz) at 500 MHz

- Available in 2.5 Clock Cycle Latency

- Two Input Clocks (K and K) for precise DDR Timing

- SRAM uses rising edges only

- Echo Clocks (CQ and CQ) simplify Data Capture in High Speed Systems

- Data Valid Pin (QVLD) to indicate Valid Data on the Output

- Single Multiplexed Address Input Bus latches Address Inputs for Read and Write Ports

- Separate Port selects for Depth Expansion

- Synchronous Internally Self-timed Writes

- QDR® II+ operates with 2.5 cycle read latency when DOFF is asserted HIGH

-...