CY7C331

CY7C331 is Asynchronous Registered EPLD manufactured by Cypress.

Features

- Twelve I/O macrocells each having:

- One state flip-flop with an XOR sum-of-products input

- One feedback flip-flop with input ing from the I/O pin

- Independent (product term) set, reset, and clock inputs on all registers

- Asynchronous bypass capability on all registers under product term control (r = s = 1)

- Global or local output enable on three-state I/O

- -

- -

- - Feedback from either register to the array 192 product terms with variable distribution to macrocells 13 inputs, 12 feedback I/O pins, plus 6 shared I/O macrocell feedbacks for a total of 31 true and plementary inputs High speed: 20 ns maximum t PD Security bit Space-saving 28-pin slim-line DIP package; also available in 28-pin PLCC

- Low power

- 90 m A typical ICC quiescent

- 180 m A ICC maximum

- UV-erasable and reprogrammable

- Programming and operation 100% testable

Functional Description

The CY7C331 is the most versatile PLD available for asynchronous designs. Central resources include twelve full D-type flip-flops with separate set, reset, and clock capability. For increased utility, XOR gates are provided at the D-inputs and the product term allocation per flip-flop is variably distributed.

I/O Resources

Pins 1 through 7 and 9 through 14 serve as array inputs; pin 14 may also be used as a global output enable for the I/O macrocell three-state outputs. Pins 15 through 20 and 23 through 28 are connected to I/O macrocells and may be managed as inputs or outputs depending on the configuration and the macrocell OE terms.

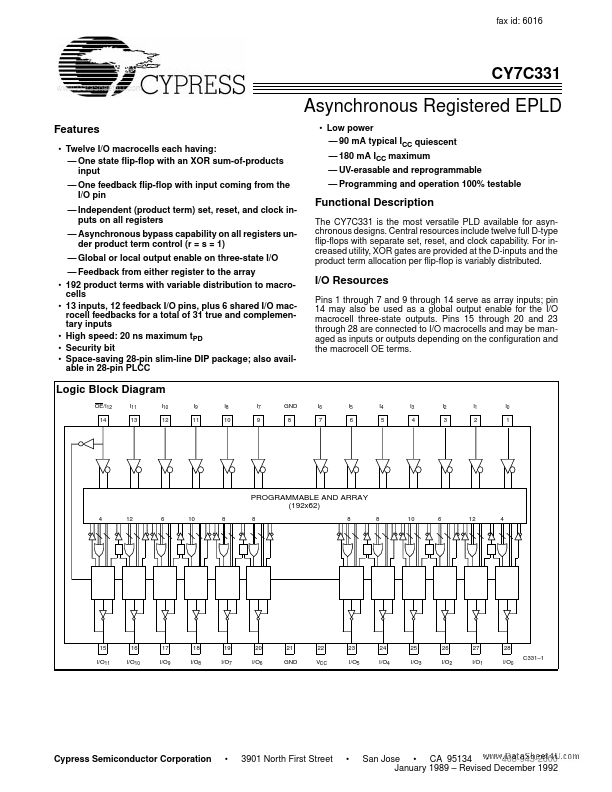

Logic Block Diagram

OE/I12 14 I11 13 I10 12 I9 11 I8 10 I7 9 GND 8 I6 7 I5 6 I4 5 I3 4 I2 3 I1 2 I0 1

PROGRAMMABLE AND ARRAY (192x62)

4 12 6 10 8 8 8 8 10 6 12 4

15 I/O11

16 I/O10

17 I/O9

18 I/O8

19 I/O7

20 I/O6

21 GND

22 VCC

23 I/O5

24 I/O4

25 I/O3

26 I/O2

27 I/O1

28 I/O0 C331- 1

Cypress Semiconductor Corporation

- 3901 North First Street

- San...