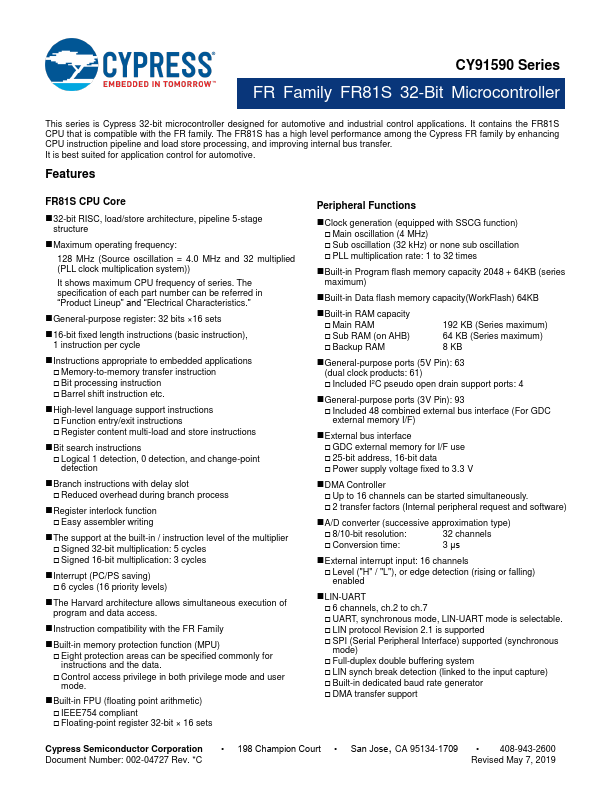

CY91590

Features

FR81S CPU Core

- 32-bit RISC, load/store architecture, pipeline 5-stage structure

- Maximum operating frequency:

128 MHz (Source oscillation = 4.0 MHz and 32 multiplied (PLL clock multiplication system))

It shows maximum CPU frequency of series. The specification of each part number can be referred in “Product Lineup” and “Electrical Characteristics.”

- General-purpose register: 32 bits ×16 sets

- 16-bit fixed length instructions (basic instruction), 1 instruction per cycle

- Instructions appropriate to embedded applications Memory-to-memory transfer instruction Bit processing instruction Barrel shift instruction etc.

- High-level language support instructions Function entry/exit instructions Register content multi-load and store instructions

- Bit search instructions Logical 1 detection, 0 detection, and change-point detection

- Branch instructions with delay slot Reduced overhead during branch process

- Register interlock function Easy assembler writing

- The support...