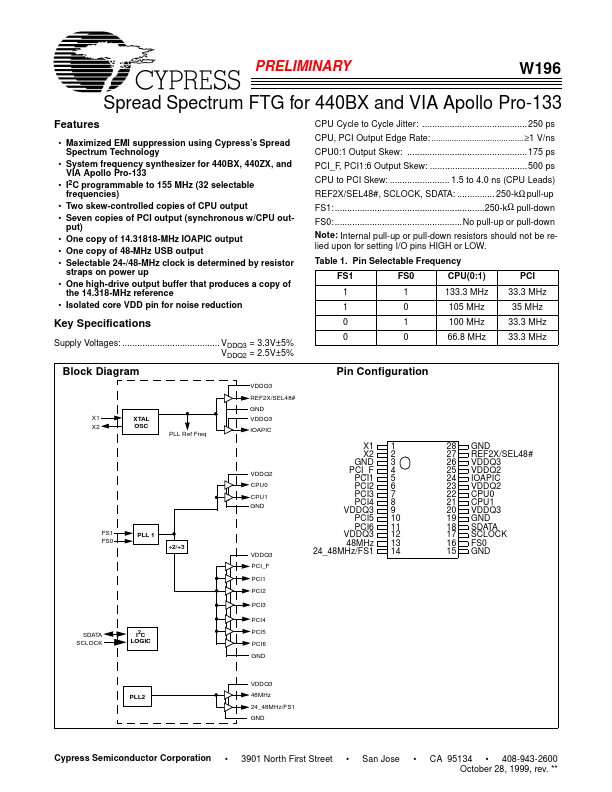

W196

Features

- Maximized EMI suppression using Cypress’s Spread Spectrum Technology

- System frequency synthesizer for 440BX, 440ZX, and VIA Apollo Pro-133

- I2C programmable to 155 MHz (32 selectable frequencies)

- Two skew-controlled copies of CPU output

- Seven copies of PCI output (synchronous w/CPU output)

- One copy of 14.31818-MHz IOAPIC output

- One copy of 48-MHz USB output

- Selectable 24-/48-MHz clock is determined by resistor straps on power up

- One high-drive output buffer that produces a copy of the 14.318-MHz reference

- Isolated core VDD pin for noise reduction CPU Cycle to Cycle Jitter: 250 ps CPU, PCI Output Edge Rate: ≥1 V/ns CPU0:1 Output Skew: 175 ps PCI_F, PCI1:6 Output Skew: 500 ps CPU to PCI Skew: 1.5 to 4.0 ns (CPU Leads) REF2X/SEL48#, SCLOCK, SDATA:...