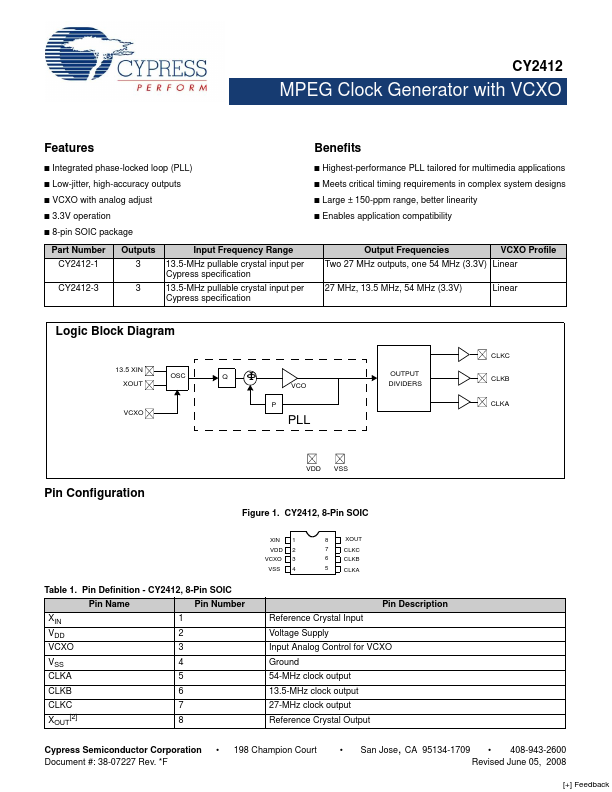

| Part | CY2412 |

|---|---|

| Description | MPEG Clock Generator |

| Manufacturer | Cypress |

| Size | 161.41 KB |

Pricing from 0.9116 USD, available from Rochester Electronics and Verical.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 2425 | 100+ : 0.9116 USD 500+ : 0.8204 USD 1000+ : 0.7566 USD 10000+ : 0.6746 USD |

View Offer |

| Verical | 2425 | 330+ : 1.1395 USD 500+ : 1.0255 USD 1000+ : 0.9458 USD 10000+ : 0.8433 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CY241V8A-01 | Cypress | MPEG Clock Generator |

| CY241V08A-12 | Cypress | Clock Generator |

| CY241V08A-01 | Cypress | MPEG Clock Generator |

| CY24119 | Cypress | MediaClock 27-MHz VCXO Clock Generator |

| CY24130 | Cypress | HOTLink II SMPTE Receiver Training Clock |