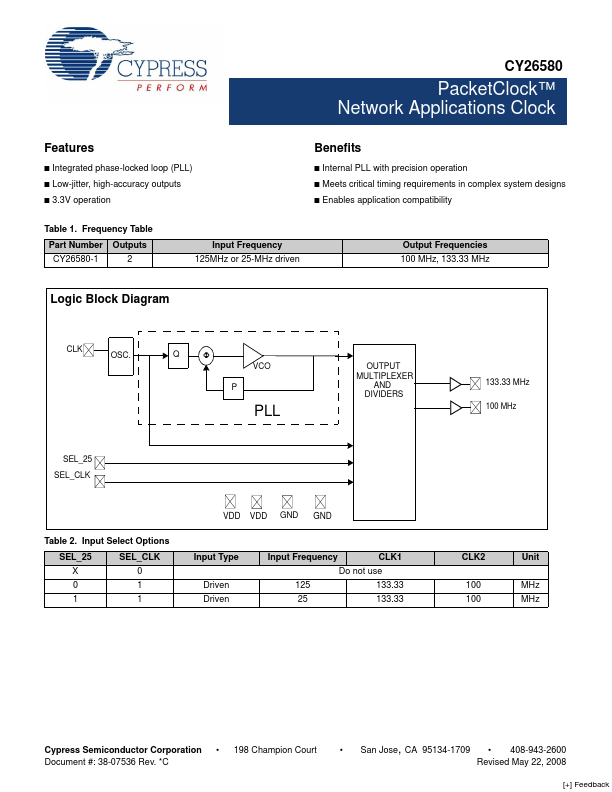

CY26580 Description

CY26580 PacketClock™ Network Applications Clock.

CY26580 Key Features

- Integrated phase-locked loop (PLL)

- Low-jitter, high-accuracy outputs

- 3.3V operation

- Internal PLL with precision operation

- Meets critical timing requirements in plex system designs

- Enables application patibility

- 198 Champion Court Document #: 38-07536 Rev. -C

- San Jose, CA 95134-1709

- 408-943-2600