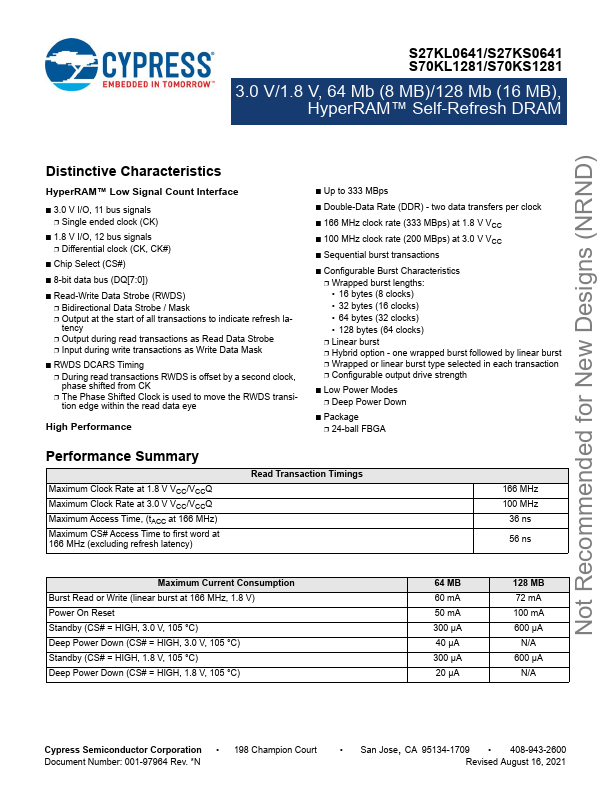

| Part | S70KS1281 |

|---|---|

| Description | Self-Refresh DRAM |

| Manufacturer | Cypress |

| Size | 1.80 MB |

Pricing from 5.39 USD, available from Rochester Electronics and Mouser.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 300 | 25+ : 5.39 USD 100+ : 5.12 USD 500+ : 4.85 USD 1000+ : 4.58 USD |

View Offer |

| Mouser | 315 | 1+ : 9.89 USD 10+ : 9.19 USD 50+ : 8.7 USD 100+ : 8.49 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| S70KS1283 | Infineon | 128Mb self-refresh DRAM |