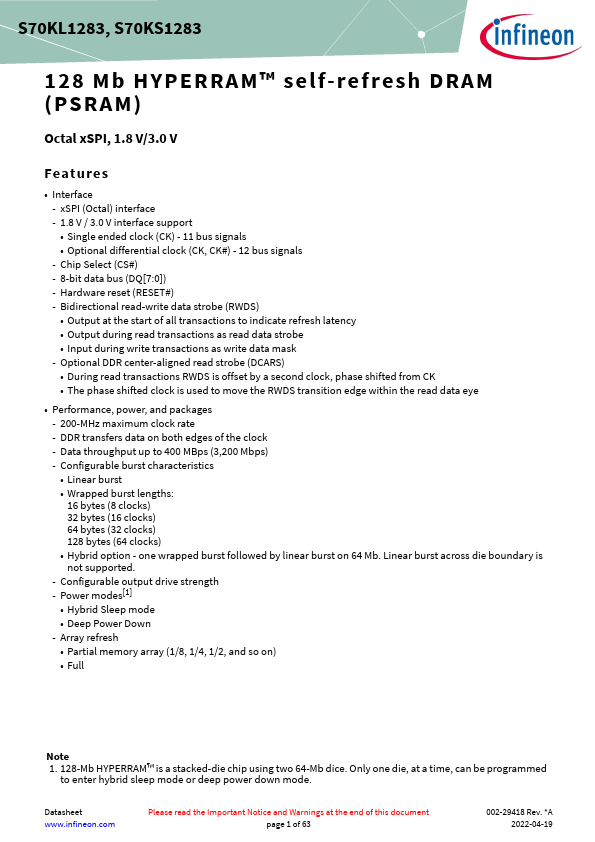

S70KS1283 Overview

Key Specifications

Operating Voltage: 1.8 V

Max Voltage (typical range): 2 V

Min Voltage (typical range): 1.7 V

Max Frequency: 200 MHz

Key Features

- xSPI (Octal) interface

- 1.8 V / 3.0 V interface support

- Single ended clock (CK)

- 11 bus signals

- Optional differential clock (CK, CK#)

- 12 bus signals

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Hardware reset (RESET#)

- Bidirectional read-write data strobe (RWDS)