PI6CB332012A

PI6CB332012A is 12-Output Low-Power Fanout Clock Buffer manufactured by Diodes Incorporated.

Description

Features

The PI6CB332012A is a low-power PCIe® 5.0/6.0 clock buffer. It takes a reference input to fanout 12 low-power differential HCSL outputs up to 400MHz, with on-chip terminations for 85Ω output impedance. An individual OE pin for each output provides easier power management. The device also supports Power Down Tolerant (PDT), automatic output clock parking upon loss of input clock, and Flexible Startup Sequencing features

.

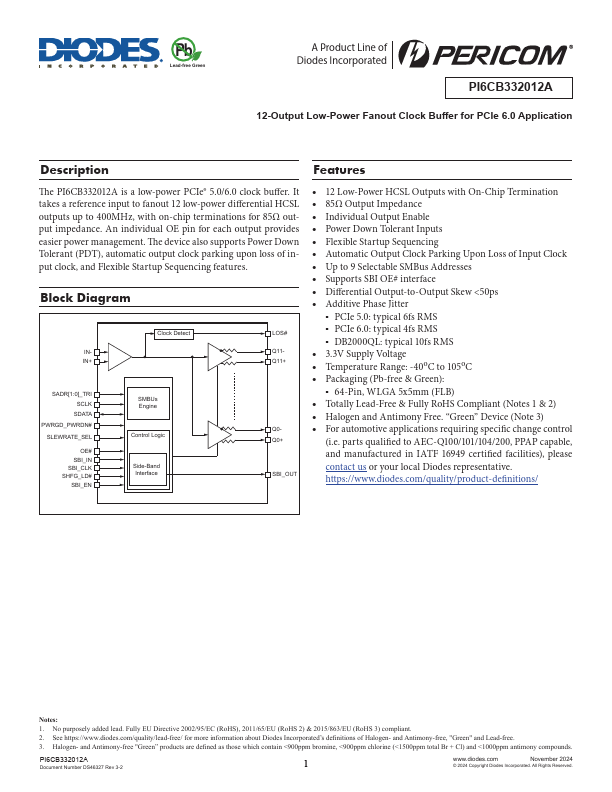

Block Diagram

ININ+

SADR[1:0]_TRI SCLK

SDATA PWRGD_PWRDN#

SLEWRATE_SEL

OE# SBI_IN SBI_CLK SHFG_LD# SBI_EN

Clock Detect

SMBUs Engine Control Logic Side-Band Interface

LOS# Q11Q11+

Q0Q0+

SBI_OUT y 12 Low-Power HCSL Outputs with On-Chip Termination y 85Ω Output Impedance y Individual Output Enable y Power Down Tolerant Inputs y Flexible Startup Sequencing y Automatic Output Clock Parking Upon Loss of Input Clock y Up to 9 Selectable SMBus Addresses y Supports SBI OE# interface y Differential Output-to-Output Skew <50ps y Additive Phase Jitter

à PCIe 5.0: typical 6fs RMS à PCIe 6.0: typical 4fs RMS à DB2000QL: typical 10fs RMS y 3.3V Supply Voltage y Temperature Range: -40o C to 105o C y Packaging (Pb-free & Green): à 64-Pin, WLGA 5x5mm (FLB) y Totally Lead-Free & Fully Ro HS pliant (Notes 1 & 2) y Halogen and Antimony Free. “Green” Device (Note 3) y For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. https://.diodes./quality/product-definitions/

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (Ro HS), 2011/65/EU (Ro HS 2) & 2015/863/EU (Ro HS 3) pliant. 2. See https://.diodes./quality/lead-free/ for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total...