DTC34LF86L

DTC34LF86L is +3.3V LVDS 24Bit Flat Panel Display (FPD) Receiver manufactured by DOESTEK.

DTC34LF8 6L/DTC34LR86L

LVDS Product DTC34LF86L/DTC34LR86L (Rev. 2.2)

+3.3V LVDS 24Bit Flat Panel Display (FPD) Receiver

- 85MHz

General Description

The D TC34LF86L/LR86L rec eivers co nvert the L VDS (Low Voltage Differential Signaling) data streams back into 28 bit s of CMOS/ TTL dat a with falling edge (DTC34LF86L) or risin g edge (DTC34LR86L) clock for convenient int erface with a variet y of L CD p anel controllers. A phase-locked transmit clock is transmitte d in p arallel with the data streams ove r a fif th L VDS link. A a transmitter (DTC34LM85L) w ill inter-o perate w ith without any translation logic. Using a 8 5 MHz clock, the dat a throu ghputs is 297.5 Mbytes/sec. This chip set is an ide al mean s to solve EMI and ca ble size problems associat ed with wide, high speed TTL interfaces.

▓

REVISED APR. 2009

Features

▓

Wide frequency range : 20 to 85 MHz shift clock support Narrow bus (10 lines) reduces cable size

▓ Sing le 3.3V supply ▓ Po wer-Down Mode ▓ ▓ ▓ ▓ ▓ ▓ ▓ ▓

Single pixel per clock XGA (1024x768) ready Supports VGA, SVGA, XGA and SXGA Up to 297.5 Megabytes/sec bandwidth Up to 2.38 Gbps throughput 300m V swing LVDS devices for low EMI PLL requires no external ponents Low profile 56-lead TSSOP package (PB Free) patible with the National DS90C386, T hine THC63LVDF84A

Falling/Rising edg e rec eiver (DT C34LF86L/LR86L)

▓ p atible with TIA/EIA-644 LVDS standard

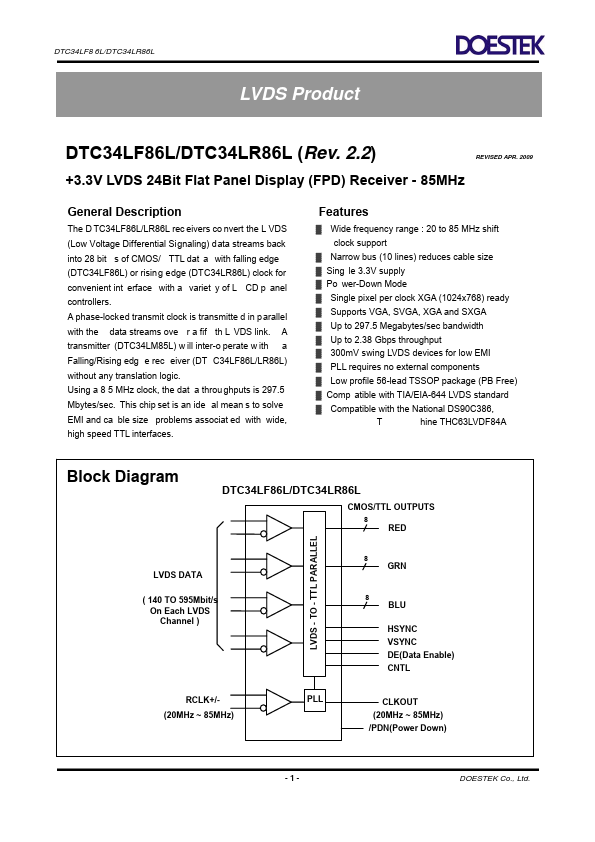

Block Diagram

DTC34LF86L/DTC34LR86L

CMOS/TTL OUTPUTS

LVDS

- TO

- TTL PARALLEL

LVDS DATA ( 140 TO 595Mbit/s On Each LVDS Channel )

BLU HSYNC VSYNC DE(Data Enable) CNTL

RCLK+/(20MHz ~ 85MHz)

CLKOUT (20MHz ~ 85MHz) /PDN(Power Down)

-1-

DOESTEK Co., Ltd. http://..

DTC34LF8 6L/DTC34LR86L

Electrical Characteristics

Vcc=3.0 ~ 3.6V @ Ta=-10 ~ +70°C CMOS/TTL DC...