PDJ2116DEBG

PDJ2116DEBG is 2G bits DDR3 SDRAM manufactured by Deutron Electronics.

- Part of the PDJ2108DEBG comparator family.

- Part of the PDJ2108DEBG comparator family.

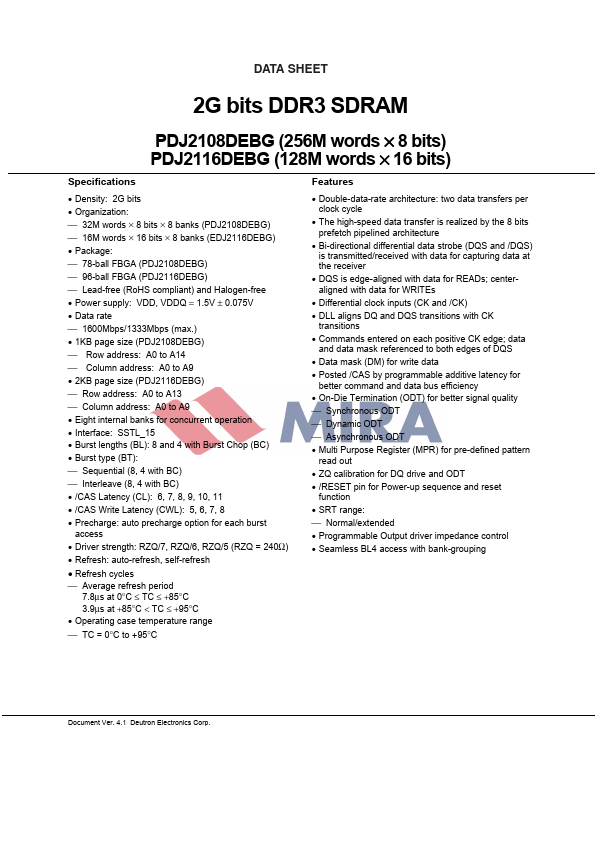

DATA SHEET

2G bits DDR3 SDRAM

PDJ2108DEBG (256M words × 8 bits) PDJ2116DEBG (128M words × 16 bits)

Specifications

- Density: 2G bits

- Organization: ⎯ 32M words × 8 bits × 8 banks (PDJ2108DEBG) ⎯ 16M words × 16 bits × 8 banks (EDJ2116DEBG)

- Package: ⎯ 78-ball FBGA (PDJ2108DEBG) ⎯ 96-ball FBGA (PDJ2116DEBG) ⎯ Lead-free (RoHS pliant) and Halogen-free

- Power supply: VDD, VDDQ = 1.5V ± 0.075V

- Data rate ⎯ 1600Mbps/1333Mbps (max.)

- 1KB page size (PDJ2108DEBG) ⎯ Row address: A0 to A14 ⎯ Column address: A0 to A9

- 2KB page size (PDJ2116DEBG) ⎯ Row address: A0 to A13 ⎯ Column address: A0 to A9

- Eight internal banks for concurrent operation

- Interface: SSTL_15

- Burst lengths (BL): 8 and...