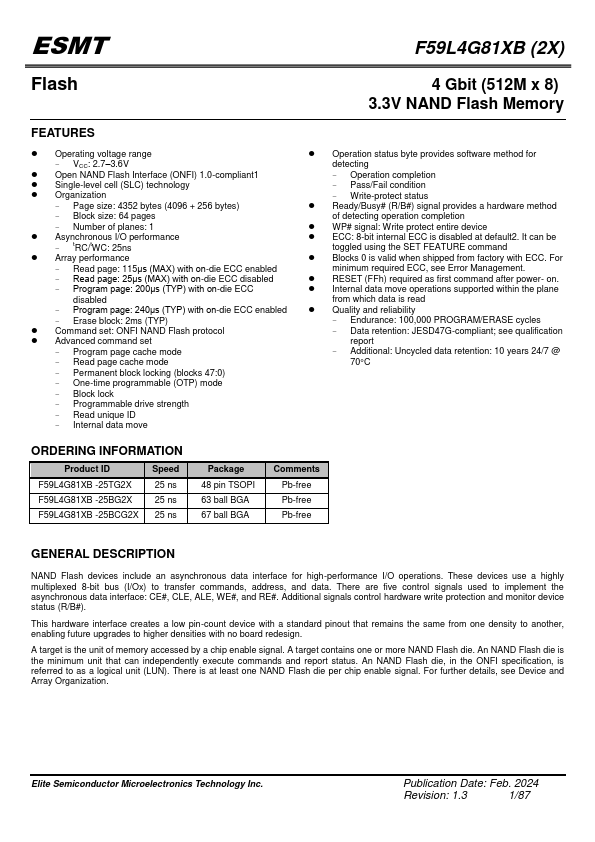

F59L4G81XB Overview

Description

NAND Flash devices include an asynchronous da.

Key Features

- Operating voltage range VCC: 2.7–3.6V

- Open NAND Flash Interface (ONFI) 1.0-compliant1

- Single-level cell (SLC) technology

- Organization Page size: 4352 bytes (4096 + 256 bytes) Block size: 64 pages Number of planes: 1

- Asynchronous I/O performance tRC/tWC: 25ns

- Command set: ONFI NAND Flash protocol

- Operation status byte provides software method for detecting Operation completion Pass/Fail condition Write-protect status

- Ready/Busy# (R/B#) signal provides a hardware method of detecting operation completion

- WP# signal: Write protect entire device

- ECC: 8-bit internal ECC is disabled at default2. It can be toggled using the SET FEATURE command