M12L64322A-6BIG2S

M12L64322A-6BIG2S is 512K x 32 Bit x 4 Banks Synchronous DRAM manufactured by Elite Semiconductor Microelectronics Technology.

- Part of the M12L64322A-5TIG2S comparator family.

- Part of the M12L64322A-5TIG2S comparator family.

FEATURES y JEDEC standard 3.3V power supply y LVTTL patible with multiplexed address y Four banks operation y MRS cycle with address key programs

- CAS Latency ( 2 & 3 )

- Burst Length ( 1, 2, 4, 8 & full page )

- Burst Type ( Sequential & Interleave ) y All inputs are sampled at the positive going edge of the system clock y Burst Read Single-bit Write operation y DQM for masking y Auto & self refresh y 64ms refresh period (4K cycle)

M12L64322A (2S)

Operation Temperature Condition -40°C~85°C

512K x 32 Bit x 4 Banks Synchronous DRAM

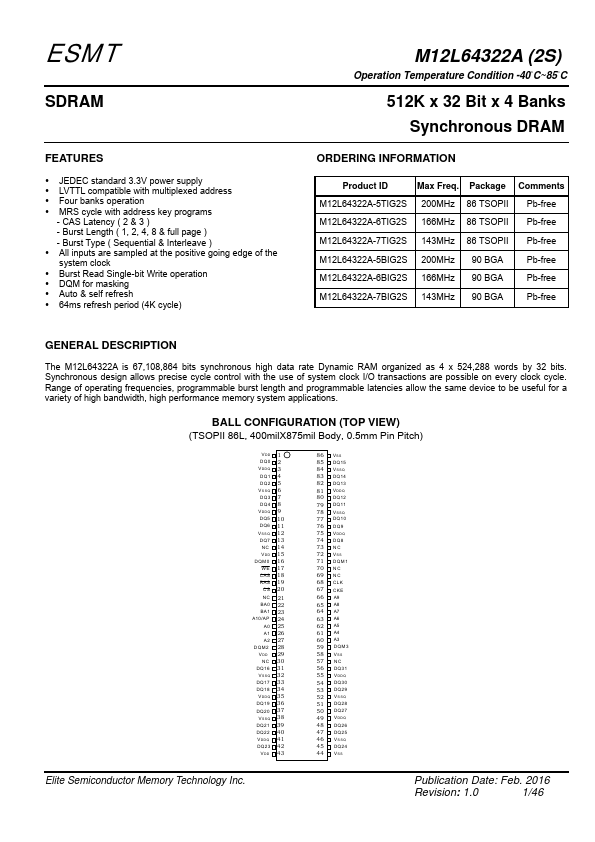

ORDERING INFORMATION

Product ID

Max Freq. Package ments

M12L64322A-5TIG2S 200MHz 86 TSOPII Pb-free

M12L64322A-6TIG2S 166MHz 86 TSOPII Pb-free

M12L64322A-7TIG2S 143MHz 86 TSOPII Pb-free

M12L64322A-5BIG2S 200MHz 90 BGA

Pb-free

M12L64322A-6BIG2S 166MHz 90 BGA

Pb-free

M12L64322A-7BIG2S 143MHz 90 BGA

Pb-free

GENERAL DESCRIPTION

The M12L64322A is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 524,288 words by 32 bits. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

BALL CONFIGURATION (TOP VIEW) (TSOPII 86L, 400mil X875mil Body, 0.5mm Pin Pitch)

VDD 1 DQ0 2 VDDQ 3 DQ1 4 DQ2 5 VSSQ 6 DQ3 7 DQ4 8 VDDQ 9 DQ5 10 DQ6 11 VSSQ 12 DQ7 13 NC 14 VDD 15 DQM0 16 WE 17 CAS 18 RAS 19

CS 20

N C 21 BA0 22 BA1 23 A10/AP 24

A0 25 A1 26 A2 27 D QM 2 28 VDD 29 NC 30 DQ16 31 VSSQ 32 DQ17 33 DQ18 34 VDDQ 35 DQ19 36 DQ20 37 VSSQ 38 DQ21 39

DQ22 40 VDDQ 41 DQ23 42

VDD 43

86 VSS 85 DQ15 84 VSSQ 83 DQ14 82 DQ13 81 VDDQ 80 DQ12 79 DQ11 78 VSSQ 77 DQ10 76 DQ9 75 VDDQ 74 DQ8 73 N C 72 VSS 71 DQM1 70 N C 69 N C 68 CLK 67 CKE

66 A9 65 A8 64 A7 63 A6 62 A5 61 A4 60 A3 59 DQM3 58 VSS

57 NC 56 DQ31 55 VDDQ 54 DQ30 53 DQ29 52 VSSQ 51 DQ28 50 DQ27 49 VDDQ 48 DQ26 47...