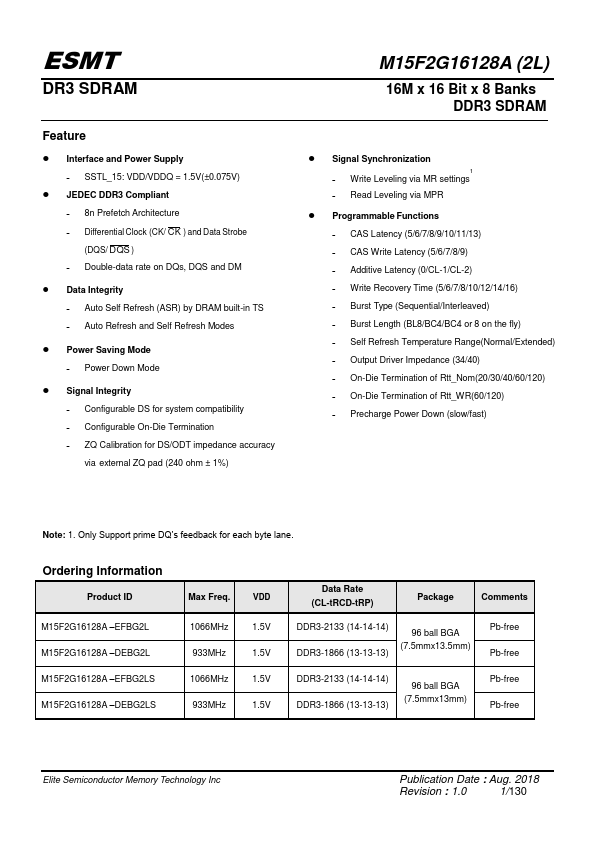

M15F2G16128A-DEBG2L

Description

The 2Gb Double-Data-Rate-3 (DDR3) DRAM is double data rate architecture to achieve high-speed operation. It is internally configured as an eight bank DRAMs.

Key Features

- Interface and Power Supply ˗ SSTL_15: VDD/VDDQ = 1.5V(±0.075V)

- JEDEC DDR3 Compliant ˗ 8n Prefetch Architecture ˗ Differential Clock (CK/ CK ) and Data Strobe (DQS/ DQS ) ˗ Double-data rate on DQs, DQS and DM

- Data Integrity ˗ Auto Self Refresh (ASR) by DRAM built-in TS ˗ Auto Refresh and Self Refresh Modes

- Power Saving Mode ˗ Power Down Mode

- Signal Integrity ˗ Configurable DS for system compatibility ˗ Configurable On-Die Termination ˗ ZQ Calibration for DS/ODT impedance accuracy via external ZQ pad (240 ohm ± 1%)