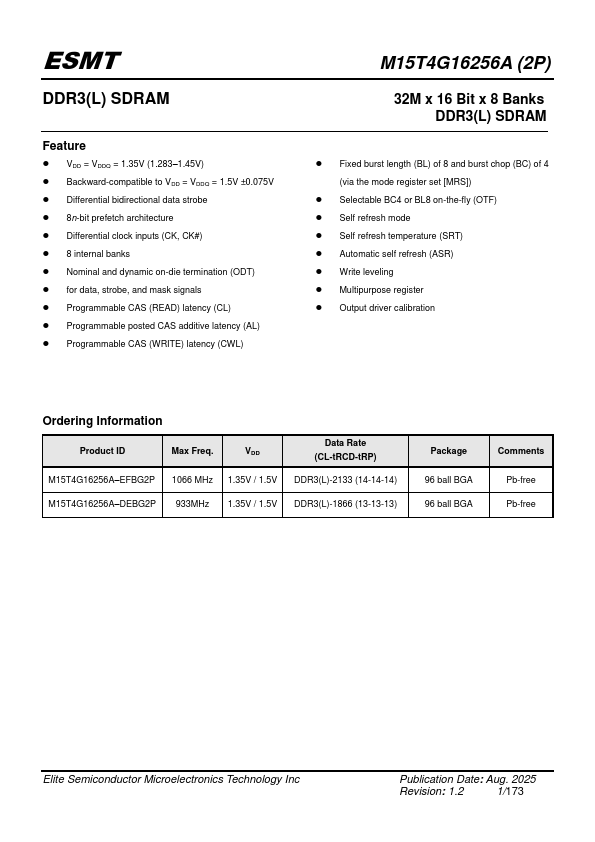

M15T4G16256A-EFBG2P

Overview

The 1.35V DDR3L SDRAM device is a low-voltage version of the 1.5V DDR3 SDRAM device. Refer to the DDR3 (1.5V) SDRAM data sheet specifications when running in 1.5V compatible mode.

- VDD = VDDQ = 1.35V (1.283-1.45V)

- Backward-compatible to VDD = VDDQ = 1.5V ±0.075V

- Differential bidirectional data strobe

- 8n-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- 8 internal banks

- Nominal and dynamic on-die termination (ODT)

- for data, strobe, and mask signals

- Programmable CAS (READ) latency (CL)

- Programmable posted CAS additive latency (AL)