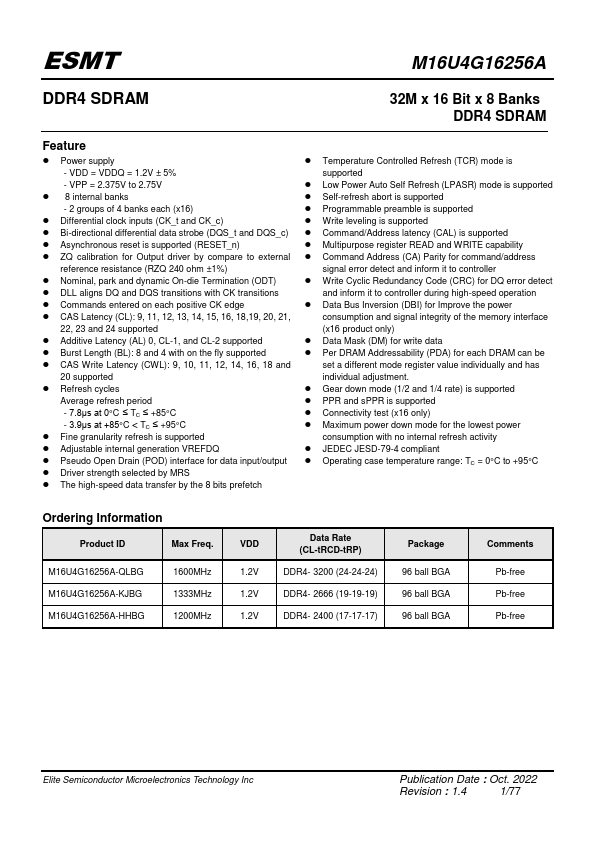

M16U4G16256A

Key Features

- Power supply - VDD = VDDQ = 1.2V ± 5% - VPP = 2.375V to 2.75V

- 8 internal banks - 2 groups of 4 banks each (x16)

- Differential clock inputs (CK_t and CK_c)

- Bi-directional differential data strobe (DQS_t and DQS_c)

- Asynchronous reset is supported (RESET_n)

- ZQ calibration for Output driver by compare to external reference resistance (RZQ 240 ohm ±1%)

- Nominal, park and dynamic On-die Termination (ODT)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge

- CAS Latency (CL): 9, 11, 12, 13, 14, 15, 16, 18,19, 20, 21, 22, 23 and 24 supported