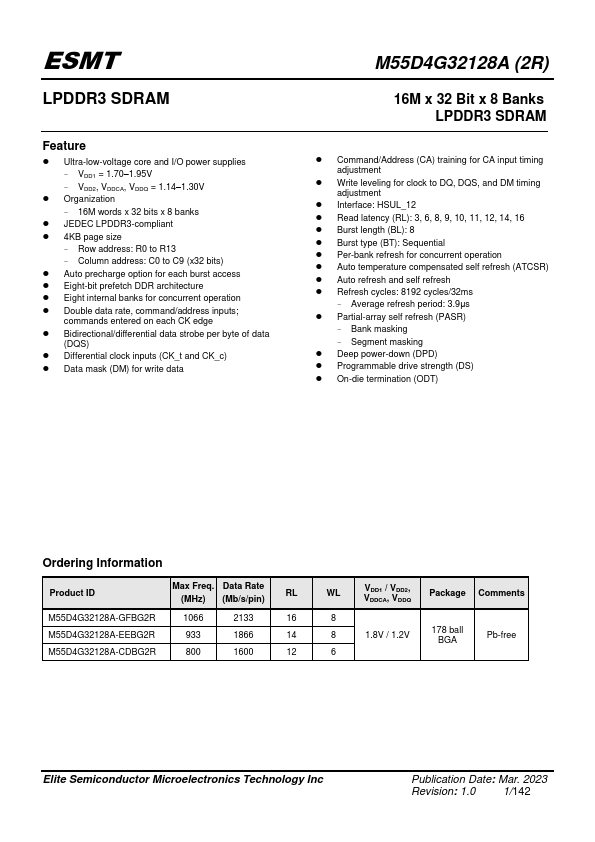

M55D4G32128A-EEBG2R

Overview

- Ultra-low-voltage core and I/O power supplies VDD1 = 1.70-1.95V VDD2, VDDCA, VDDQ = 1.14-1.30V

- Organization 16M words x 32 bits x 8 banks

- JEDEC LPDDR3-compliant

- 4KB page size Row address: R0 to R13 Column address: C0 to C9 (x32 bits)

- Auto precharge option for each burst access

- Eight-bit prefetch DDR architecture

- Eight internal banks for concurrent operation

- Double data rate, command/address inputs; commands entered on each CK edge

- Bidirectional/differential data strobe per byte of data (DQS)

- Differential clock inputs (CK_t and CK_c)