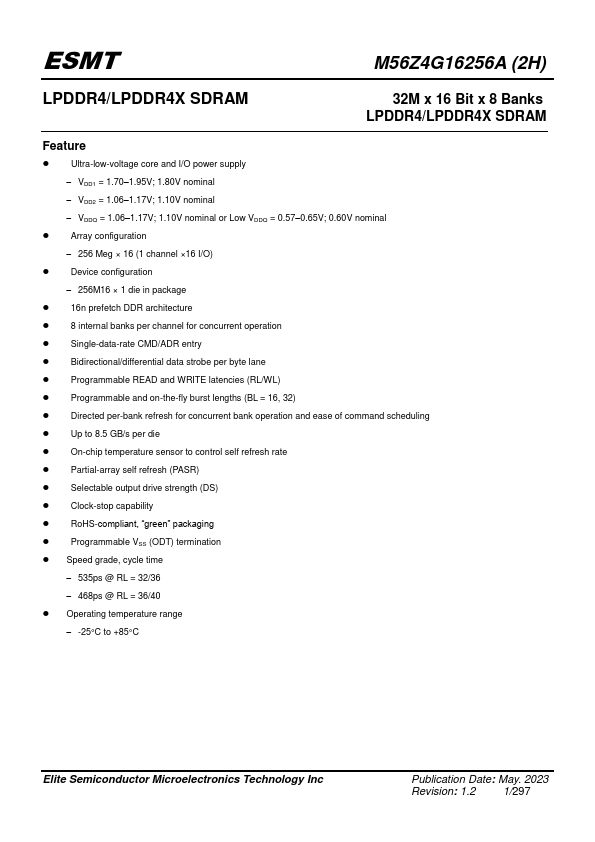

M56Z4G16256A-SMBYG2H

Key Features

- Array configuration – 256 Meg × 16 (1 channel ×16 I/O)

- Device configuration – 256M16 × 1 die in package

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL = 16

- Directed per-bank refresh for concurrent bank operation and ease of mand scheduling

- Up to 8.5 GB/s per die