CP80S54

CP80S54 is EPROM/ROM-Based 8-Bit Microcontroller Series manufactured by Unknown Manufacturer.

FEATURES

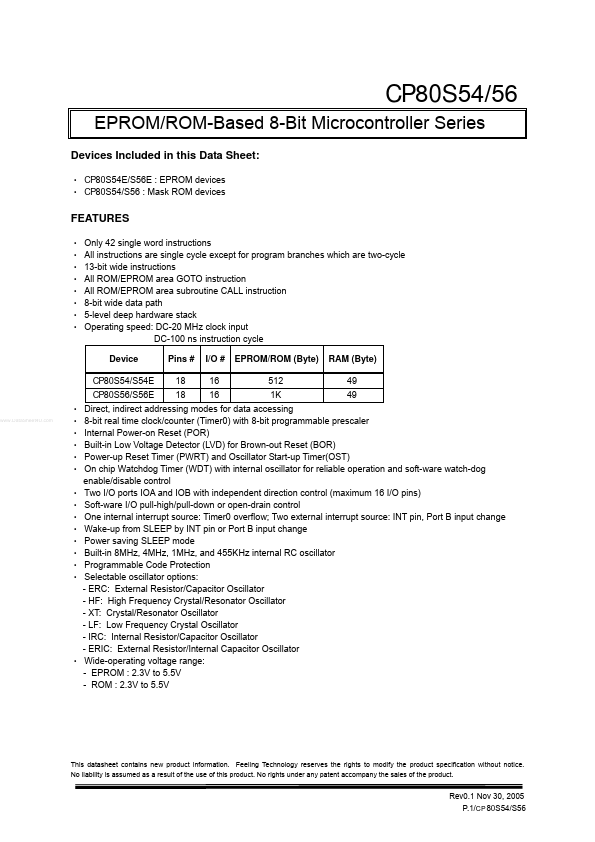

‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ Only 42 single word instructions All instructions are single cycle except for program branches which are two-cycle 13-bit wide instructions All ROM/EPROM area GOTO instruction All ROM/EPROM area subroutine CALL instruction 8-bit wide data path 5-level deep hardware stack Operating speed: DC-20 MHz clock input DC-100 ns instruction cycle Device CP80S54/S54E CP80S56/S56E

..

Pins # 18 18

I/O # 16 16

EPROM/ROM (Byte) 512 1K

RAM (Byte) 49 49

‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧ ‧

‧

Direct, indirect addressing modes for data accessing 8-bit real time clock/counter (Timer0) with 8-bit programmable prescaler Internal Power-on Reset (POR) Built-in Low Voltage Detector (LVD) for Brown-out Reset (BOR) Power-up Reset Timer (PWRT) and Oscillator Start-up Timer(OST) On chip Watchdog Timer (WDT) with internal oscillator for reliable operation and soft-ware watch-dog enable/disable control Two I/O ports IOA and IOB with independent direction control (maximum 16 I/O pins) Soft-ware I/O pull-high/pull-down or open-drain control One internal interrupt source: Timer0 overflow; Two external interrupt source: INT pin, Port B input change Wake-up from SLEEP by INT pin or Port B input change Power saving SLEEP mode Built-in 8MHz, 4MHz, 1MHz, and 455KHz internal RC oscillator Programmable Code Protection Selectable oscillator options:

- ERC: External Resistor/Capacitor Oscillator

- HF: High Frequency Crystal/Resonator Oscillator

- XT: Crystal/Resonator Oscillator

- LF: Low Frequency Crystal Oscillator

- IRC: Internal Resistor/Capacitor Oscillator

- ERIC: External Resistor/Internal Capacitor Oscillator Wide-operating voltage range:

- EPROM : 2.3V to 5.5V

- ROM : 2.3V to 5.5V

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent acpany the sales of the product.

Rev0.1 Nov 30, 2005 P.1/CP...