EN29F040 Overview

Key Specifications

Operating Voltage: 5 V

Max Operating Temp: 70 °C

Min Operating Temp: 0 °C

Description

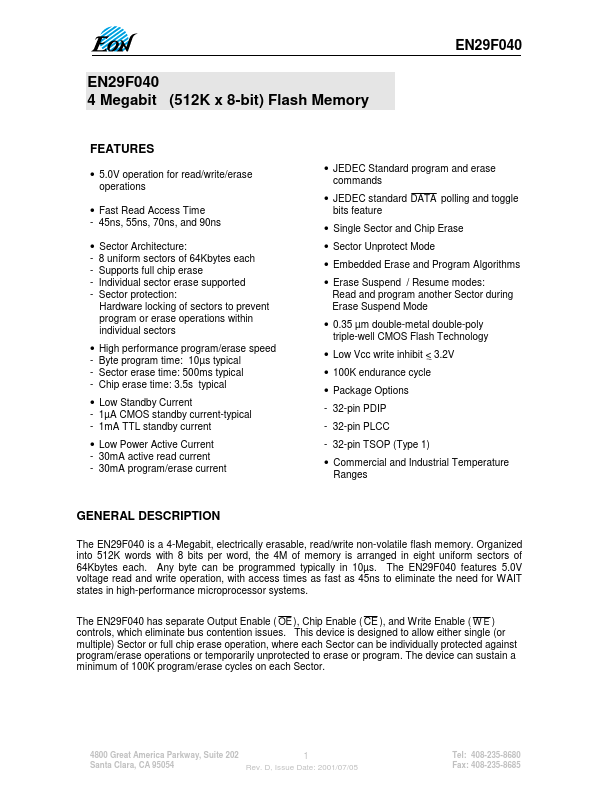

The EN29F040 is a 4-Megabit, electrically erasable, read/write non-volatile flash memory. Organized into 512K words with 8 bits per word, the 4M of memory is arranged in eight uniform sectors of 64Kbytes each.

Key Features

- 5.0V operation for read/write/erase operations

- Fast Read Access Time

- 45ns, 55ns, 70ns, and 90ns

- JEDEC Standard program and erase commands

- JEDEC standard DATA polling and toggle bits feature