HM63921

HM63921 is 2048-word x 9-bit CMOS Parallel In-Out FIFO Memory manufactured by Unknown Manufacturer.

eatures

- -

- -

- -

- -

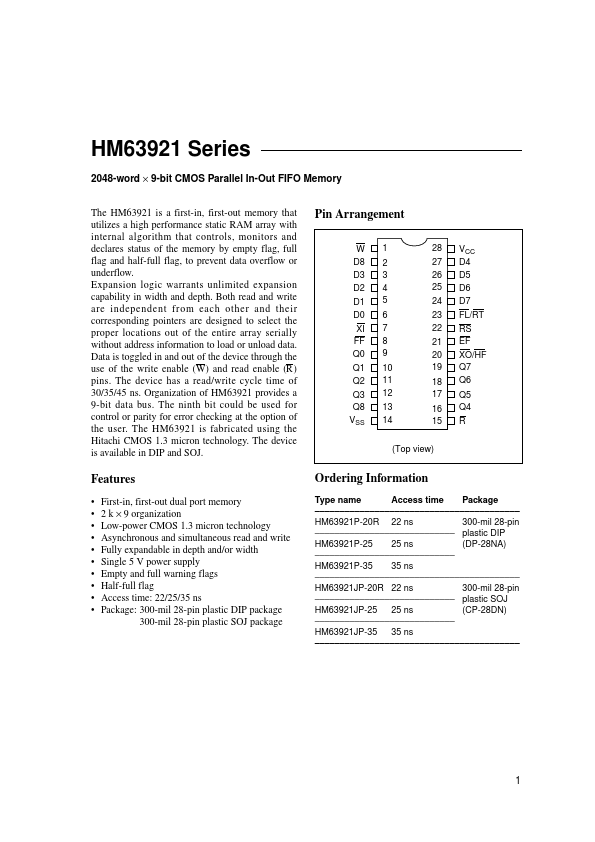

- - First-in, first-out dual port memory 2 k × 9 organization Low-power CMOS 1.3 micron technology Asynchronous and simultaneous read and write Fully expandable in depth and/or width Single 5 V power supply Empty and full warning flags Half-full flag Access time: 22/25/35 ns Package: 300-mil 28-pin plastic DIP package 300-mil 28-pin plastic SOJ package

Ordering Information

Type name HM63921P-20R HM63921P-25 HM63921P-35 Access time 22 ns 25 ns 35 ns 300-mil 28-pin (CP-28DN) Package 300-mil 28-pin (DP-28NA)

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

- -

-...