Datasheet Summary

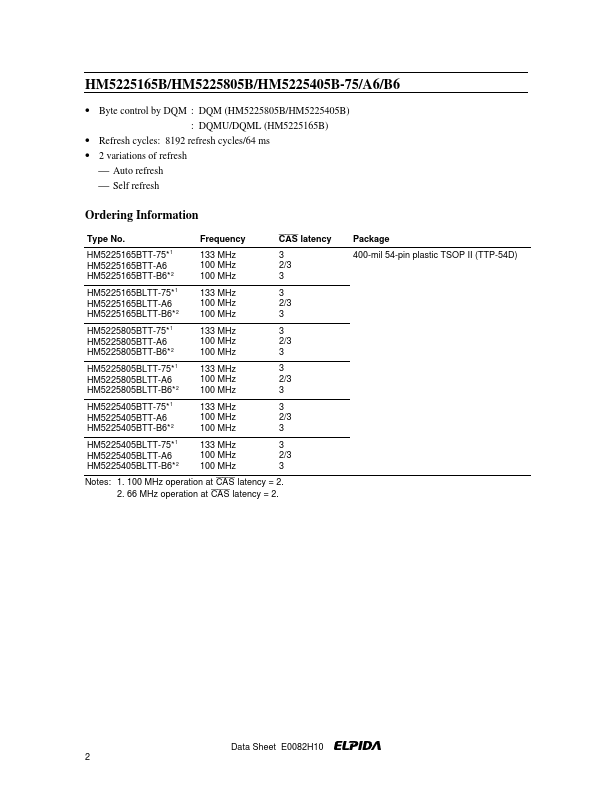

HM5225165B-75/A6/B6 HM5225805B-75/A6/B6 HM5225405B-75/A6/B6

256M LVTTL interface SDRAM 133 MHz/100 MHz 4-Mword × 16-bit × 4-bank/8-Mword × 8-bit × 4-bank /16-Mword × 4-bit × 4-bank PC/133, PC/100 SDRAM

E0082H10 (1st edition) (Previous ADE-203-1073B (Z)) Jan. 31, 2001 Description

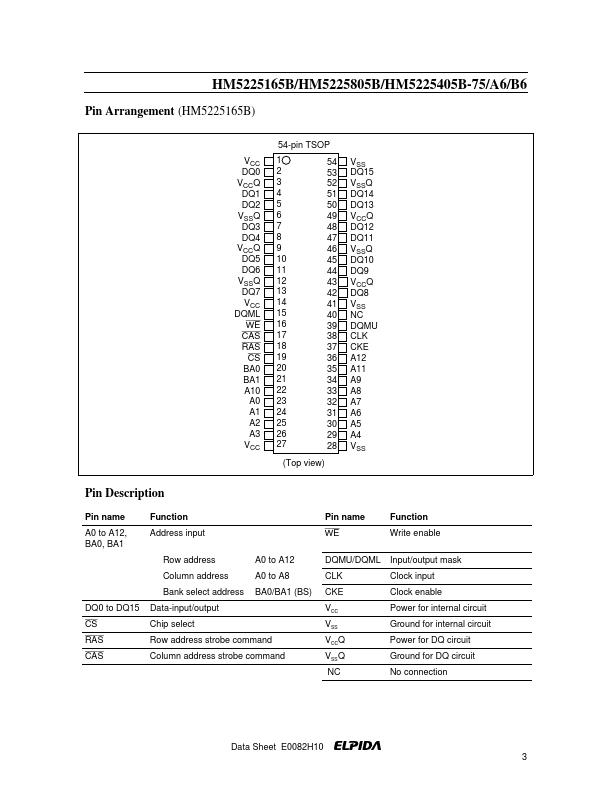

The HM5225165B is a 256-Mbit SDRAM organized as 4194304-word × 16-bit × 4 bank. The HM5225805B is a 256-Mbit SDRAM organized as 8388608-word × 8-bit × 4 bank. The HM5225405B is a 256-Mbit SDRAM organized as 16777216-word × 4-bit × 4 bank. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54-pin plastic TSOP II.

Features

- -

- -

- -

- - 3.3 V power supply Clock...