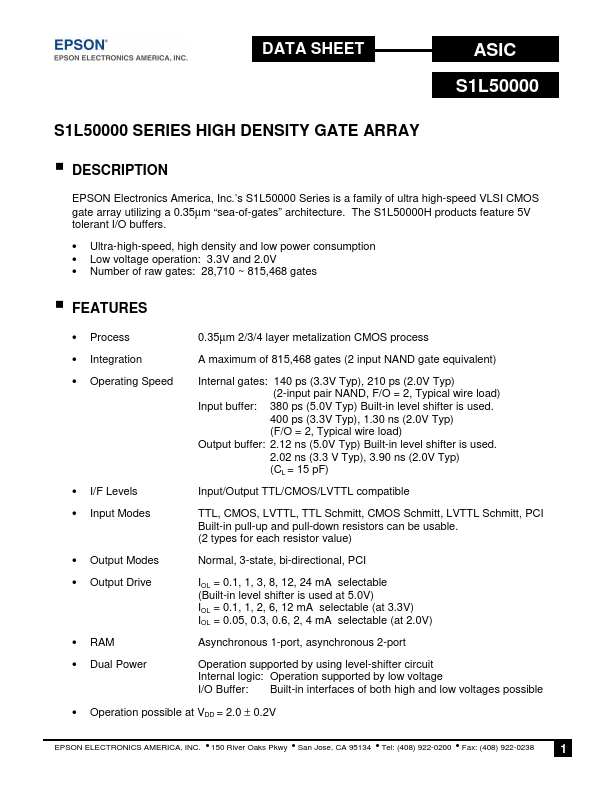

S1L50000 Overview

Description

EPSON Electronics America, Inc.’s S1L50000 Series is a family of ultra high-speed VLSI CMOS gate array utilizing a 0.35µm “sea-of-gates” architecture. The S1L50000H products feature 5V tolerant I/O buffers.

Key Features

- I/F Levels Input Modes

- Output Modes Output Drive

- RAM Dual Power