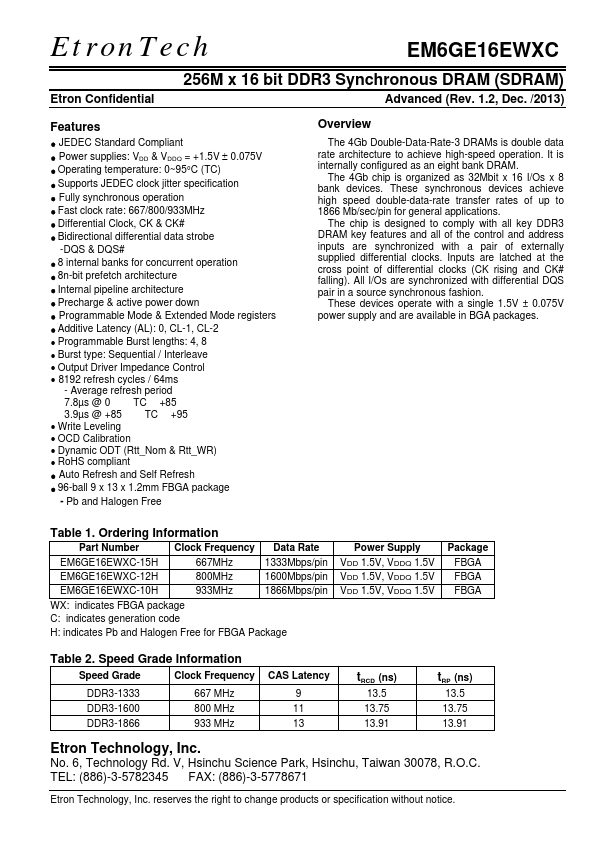

| Part | EM6GE16EWXC |

|---|---|

| Description | 256M x 16 bit DDR3 Synchronous DRAM |

| Manufacturer | EtronTech |

| Size | 815.66 KB |

Pricing from 5.7352 USD, available from Win Source and SHENGYU ELECTRONICS.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Win Source | 1606 | 9+ : 5.7352 USD 22+ : 4.7059 USD 33+ : 4.5588 USD 46+ : 4.4117 USD |

View Offer |

| SHENGYU ELECTRONICS | 10957 | 1+ : 2.4502 USD 10+ : 2.4012 USD 100+ : 2.33 USD 1000+ : 2.25 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| EM6GE16EWAKG | Etron Technology | 256M x 16 bit DDR3 Synchronous DRAM |