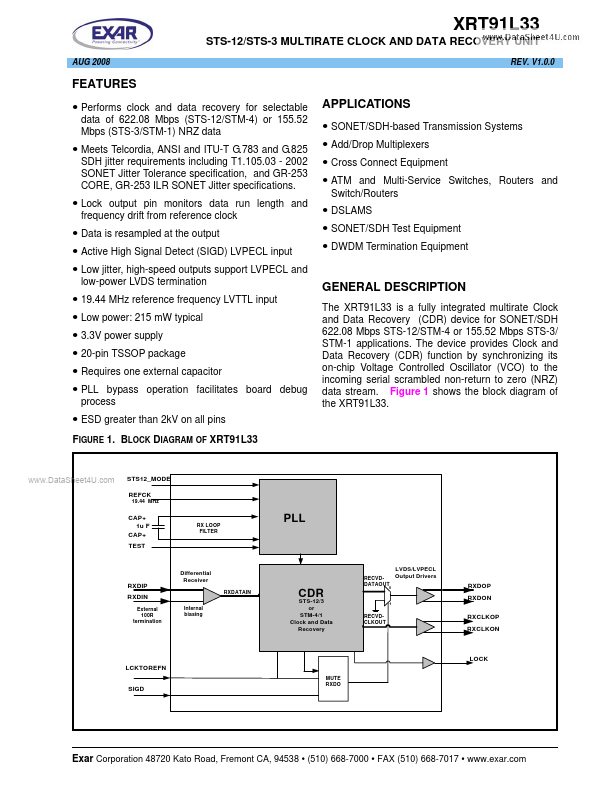

| Part | XRT91L33 |

|---|---|

| Description | STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

| Manufacturer | Exar |

| Size | 535.51 KB |

Pricing from 4.088 USD, available from Verical and Flip Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Verical | 1560 | 192+ : 4.088 USD | View Offer |

| Flip Electronics | 1562 | - | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| XRT91L33A | Exar | STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |