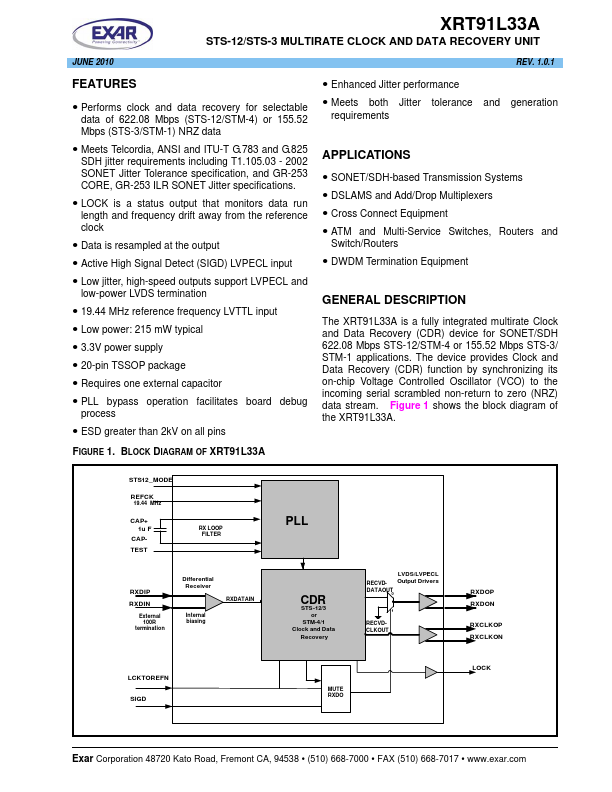

XRT91L33A Overview

Key Specifications

Package: TSSOP

Pins: 20

Operating Voltage: 3.3 V

Length: 6.5 mm

Key Features

- Performs clock and data recovery for selectable data of 622.08 Mbps (STS-12/STM-4) or 155.52 Mbps (STS-3/STM-1) NRZ data

- LOCK is a status output that monitors data run length and frequency drift away from the reference clock

- Data is resampled at the output

- Active High Signal Detect (SIGD) LVPECL input

- Low jitter, high-speed outputs support LVPECL and low-power LVDS termination